Springer-Lehrbuch

---

Th. Tille • D. Schmitt-Landsiedel

# Mikroelektronik

Halbleiterbauelemente und deren Anwendung in

elektronischen Schaltungen

Mit 243 Abbildungen

Springer

**Dr.-Ing. Thomas Tille**

Technische Universität München

Arcisstr. 21

80333 München

BMW AG

Knorrstr. 147

80788 München

**Prof. Dr. rer. nat. Doris Schmitt-Landsiedel**

Technische Universität München

Arcisstr. 21

80333 München

ISBN 3-540-20422-9 Springer-Verlag Berlin Heidelberg New York

Bibliografische Information der Deutschen Bibliothek

Die Deutsche Bibliothek verzeichnet diese Publikation in der Deutschen Nationalbibliografie;

detaillierte bibliografische Daten sind im Internet über <http://dnb.ddb.de> abrufbar.

Dieses Werk ist urheberrechtlich geschützt. Die dadurch begründeten Rechte, insbesondere die der Übersetzung, des Nachdrucks, des Vortrags, der Entnahme von Abbildungen und Tabellen, der Funksendung, der Mikroverfilmung oder Vervielfältigung auf anderen Wegen und der Speicherung in Datenverarbeitungsanlagen, bleiben, auch bei nur auszugsweiser Verwertung, vorbehalten. Eine Vervielfältigung dieses Werkes oder von Teilen dieses Werkes ist auch im Einzelfall nur in den Grenzen der gesetzlichen Bestimmungen des Urheberrechtsgesetzes der Bundesrepublik Deutschland vom 9. September 1965 in der jeweils geltenden Fassung zulässig. Sie ist grundsätzlich vergütungspflichtig. Zu widerhandlungen unterliegen den Strafbestimmungen des Urheberrechtsgesetzes.

Springer ist ein Unternehmen von Springer Science+Business Media

[springer.de](http://springer.de)

© Springer-Verlag Berlin Heidelberg 2005

Printed in Germany

Die Wiedergabe von Gebrauchsnamen, Handelsnamen, Warenbezeichnungen usw. in diesem Buch berechtigt auch ohne besondere Kennzeichnung nicht zu der Annahme, dass solche Namen im Sinne der Warenzeichen- und Markenschutz-Gesetzgebung als frei zu betrachten wären und daher von jedermann benutzt werden dürften. Sollte in diesem Werk direkt oder indirekt auf Gesetze, Vorschriften oder Richtlinien (z. B. DIN, VDI, VDE) Bezug genommen oder aus ihnen zitiert worden sein, so kann der Verlag keine Gewähr für die Richtigkeit, Vollständigkeit oder Aktualität übernehmen. Es empfiehlt sich, gegebenenfalls für die eigenen Arbeiten die vollständigen Vorschriften oder Richtlinien in der jeweils gültigen Fassung hinzuzuziehen.

Satz: Gelieferte Daten des Autors

Einbandgestaltung: medionet AG, Berlin

Gedruckt auf säurefreiem Papier

7/3020/M - 5 4 3 2 1 0

# Vorwort

Die Mikroelektronik stellt mit ihren innovativen Entwicklungen und breiten Anwendungsmöglichkeiten einen wichtigen Wirtschaftsfaktor in der heutigen Zeit dar, dessen Bedeutung mehr und mehr zunimmt. Auf Grund der wachsenden Komplexität in der Mikroelektronik ist die Kenntnis der Wirkungsweise von Halbleiterbauelementen und deren Nutzung in elektronischen Schaltungen von großer Bedeutung.

Dieses Buch vermittelt die wichtigsten Themengebiete der Mikroelektronik in prägnanter Form. Es gestattet dem Leser, das Verständnis für den Aufbau und die Funktionsweise elektronischer Halbleiterbauelemente der Mikroelektronik zu erlangen und den Einsatz in schaltungstechnischen Anwendungen kennen zu lernen. Dabei steht die Verknüpfung physikalischer Halbleiter-Effekte mit der Funktionsweise elektronischer Bauelemente und integrierter Schaltungen im Vordergrund. Durch die Vielfalt und Beschreibungsweise der behandelten elektronischen Halbleiterbauelemente und deren Anwendungsmöglichkeiten wird ein umfassendes Bild des Stoffgebietes geliefert.

Der Inhalt des Buches erstreckt sich über die Gebiete Halbleiter-Grundlagen, Halbleiterdioden, Bipolar- und Feldeffekttransistoren sowie Leistungsbauelemente, Halbleitersensoren und Integrierte Schaltungen. Die Halbleiter-Grundlagen umfassen u.a. das Bindungs- und Bändermodell, Relaxationsprozesse, den Ladungsträgertransport und weitere Halbleitereffekte. Die Gebiete Halbleiterdioden, Bipolar- und Feldeffekttransistoren beinhalteten jeweils den Aufbau, die Wirkungsweise, die Strom-Spannungs-Charakteristika und technologische Realisierung dieser elektronischen Bauelemente sowie die zugehörigen Netzwerkmodelle, das Schaltverhalten und die wesentlichen Grundschaltungen. Des Weiteren werden Leistungsbauelemente an Hand der wichtigsten Vertreter hinsichtlich ihrer Eigenschaften und Anwendbarkeit beschrieben. Aus dem Gebiet der Halbleitersensoren werden Temperatur-, Magneto-, Opto- und Chemosensoren sowie Sensoren für mechanische Größen betrachtet. Im Kapitel Integrierte Schaltungen wird auf die statische und dynamische CMOS-Logik sowie auf CMOS-Speicherschaltungen und integrierte Logikbausteine eingegangen.

Das Buch eignet sich als vorlesungsbegleitendes Lehrbuch an Universitäten und Fachhochschulen, zum Selbststudium und als hilfreiches Kompendium im Beruf. Es richtet sich sowohl an Studierende der Ingenieur- und Naturwissenschaften im Hauptstudium, als auch an Professionals in Wissenschaft und Wirtschaft.

# Inhaltsverzeichnis

|                                                                    |      |

|--------------------------------------------------------------------|------|

| <b>Formelzeichen und Naturkonstanten .....</b>                     | XIII |

| <b>1 Halbleiter-Grundlagen.....</b>                                | 1    |

| 1.1 Halbleitermaterialien.....                                     | 1    |

| 1.2 Bindungsmodell.....                                            | 3    |

| 1.2.1 Gitterstruktur .....                                         | 3    |

| 1.2.2 Eigenleitung .....                                           | 4    |

| 1.2.3 Störstellenleitung .....                                     | 7    |

| 1.3 Bändermodell.....                                              | 8    |

| 1.3.1 Aufbau des Bändermodells.....                                | 9    |

| 1.3.2 Bänderstruktur im Energie-Impuls-Raum .....                  | 11   |

| 1.3.3 Bänderbesetzung.....                                         | 11   |

| 1.3.3.1 Zustandsdichte .....                                       | 12   |

| 1.3.3.2 Besetzungswahrscheinlichkeit .....                         | 12   |

| 1.3.3.3 Ladungsträgerverteilung.....                               | 13   |

| 1.3.4 Entartete Halbleiter .....                                   | 15   |

| 1.4 Ladungsträgertransport.....                                    | 16   |

| 1.4.1 Driftstromdichte.....                                        | 16   |

| 1.4.2 Diffusionsstromdichte .....                                  | 18   |

| 1.4.3 Konvektionsstromdichte.....                                  | 19   |

| 1.5 Halbleiter im Nichtgleichgewicht .....                         | 20   |

| 1.5.1 Majoritätsträgerinjektion .....                              | 20   |

| 1.5.2 Minoritätsträgerinjektion .....                              | 21   |

| 1.5.3 Minoritäts- und Majoritätsträgerinjektion .....              | 22   |

| 1.5.4 Minoritätsträgerdiffusion .....                              | 24   |

| 1.5.5 Ladungsträgerbilanz.....                                     | 26   |

| 1.6 Weitere Halbleitereffekte .....                                | 27   |

| 1.6.1 Lawineneffekt .....                                          | 27   |

| 1.6.2 Thermoeffekt .....                                           | 28   |

| 1.6.2.1 Thermospannung im homogenen Halbleiter .....               | 28   |

| 1.6.2.1 Thermospannung zwischen verschiedenen Materialien.....     | 29   |

| 1.6.3 Halleffekt .....                                             | 29   |

| <b>2 Halbleiterdioden.....</b>                                     | 32   |

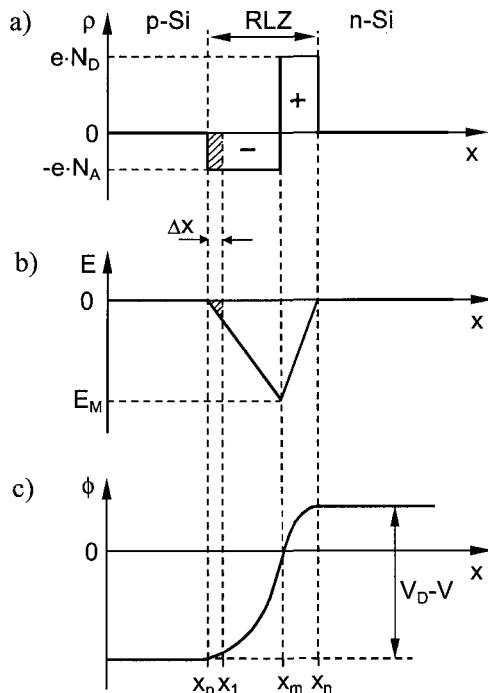

| 2.1 pn-Übergang .....                                              | 32   |

| 2.1.1 Abrupter pn-Übergang im thermodynamischen Gleichgewicht..... | 32   |

|                                                                 |           |

|-----------------------------------------------------------------|-----------|

| 2.1.2 Abrupter pn-Übergang unter Vorspannung .....              | 35        |

| 2.1.2.1 Raumladungszone des pn-Übergangs.....                   | 36        |

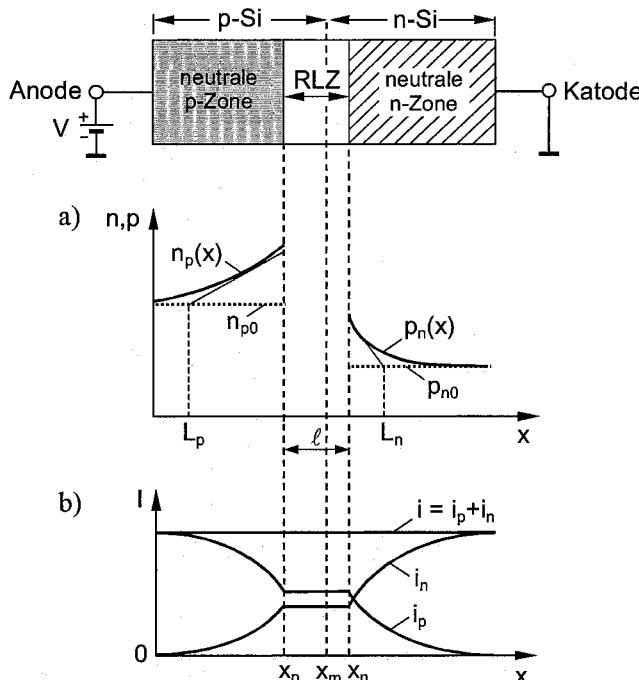

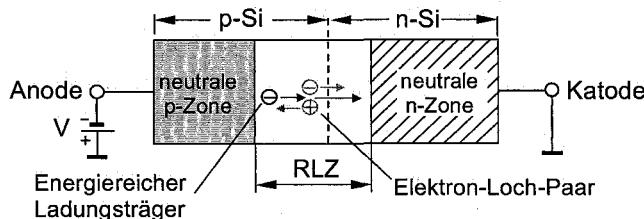

| 2.1.2.2 pn-Übergang in Flusspolung .....                        | 38        |

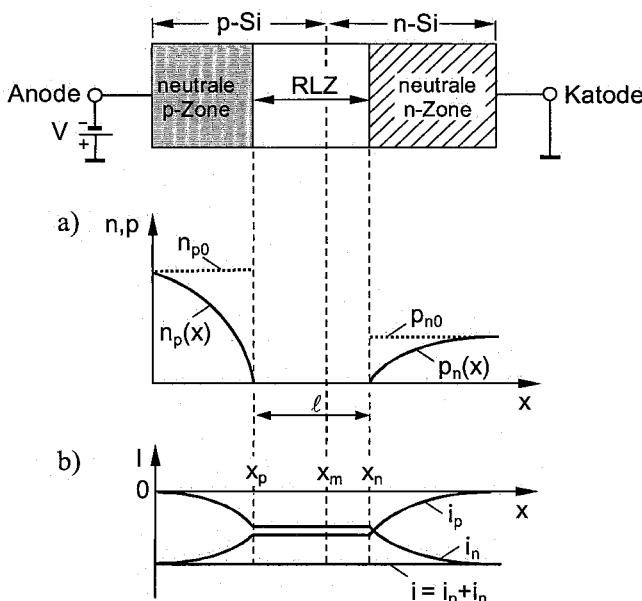

| 2.1.2.3 pn-Übergang in Sperrpolung .....                        | 41        |

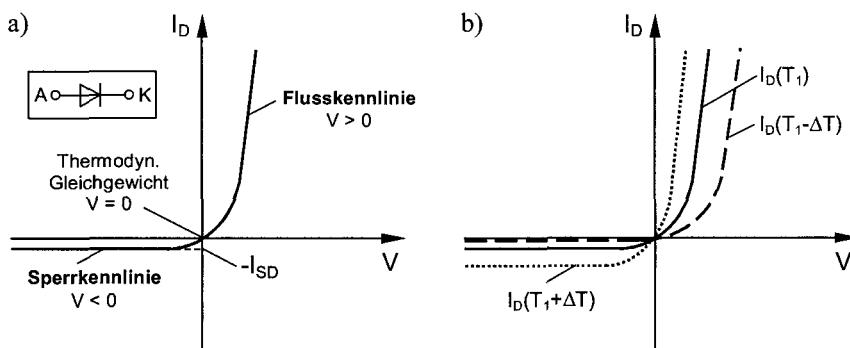

| 2.2 Diodenkennlinien.....                                       | 42        |

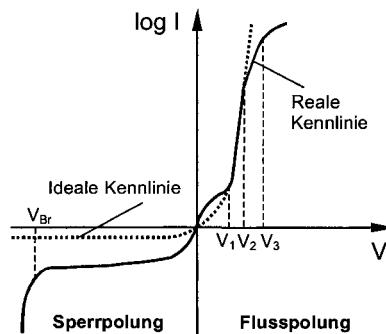

| 2.2.1 Kennlinie der idealen Diode .....                         | 42        |

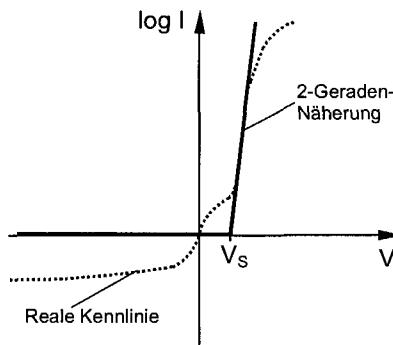

| 2.2.2 Kennlinie der realen Diode.....                           | 43        |

| 2.2.3 Diodenkennlinie mit 2-Geraden-Näherung .....              | 43        |

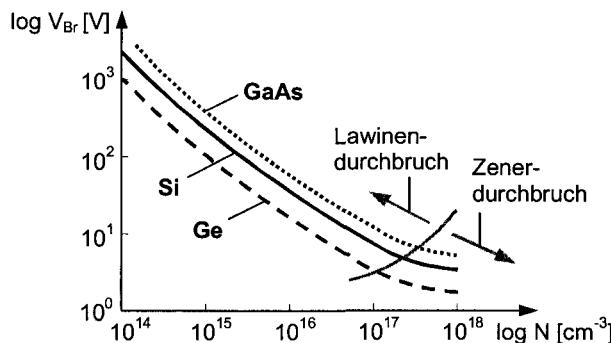

| 2.3 Durchbruchsmechanismen .....                                | 44        |

| 2.2.1 Lawineneffekt.....                                        | 44        |

| 2.2.2 Zenereffekt .....                                         | 46        |

| 2.2.3 Thermischer Durchbruch.....                               | 46        |

| 2.4 Technologische Realisierung.....                            | 47        |

| 2.5 Netzwerkmodelle der pn-Diode .....                          | 48        |

| 2.5.1 Sperrsicht- und Diffusionskapazität .....                 | 48        |

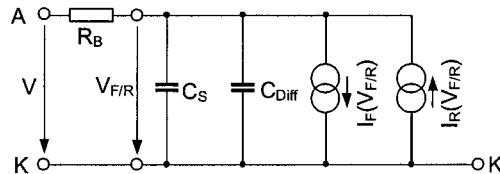

| 2.5.2 Großsignalersatzschaltbild .....                          | 50        |

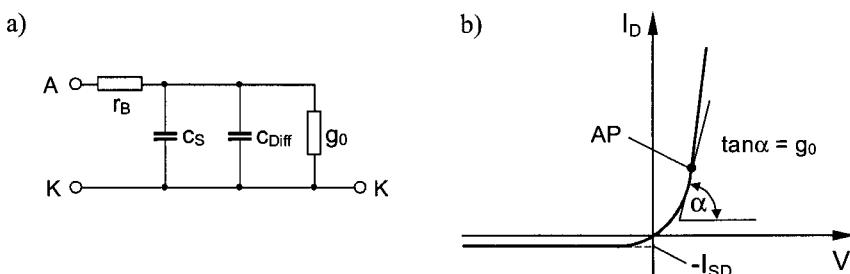

| 2.5.3 Kleinsignalersatzschaltbild.....                          | 50        |

| 2.6 Schaltverhalten der pn-Diode .....                          | 51        |

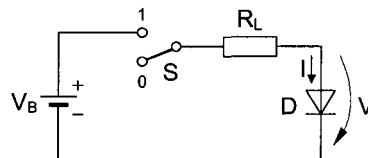

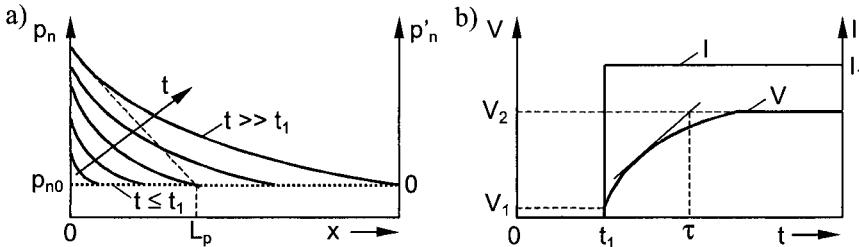

| 2.6.1 Schalten ohmscher Lasten.....                             | 51        |

| 2.6.2 Schalten induktiver Lasten .....                          | 53        |

| 2.7 Diodentypen .....                                           | 54        |

| 2.7.1 pin-Diode .....                                           | 54        |

| 2.7.2 Z-Diode .....                                             | 57        |

| 2.7.3 Tunneldiode.....                                          | 58        |

| 2.7.4 Schottky-Diode.....                                       | 59        |

| 2.7.5 Kapazitätsdiode .....                                     | 61        |

| 2.7.6 Fotodiode .....                                           | 62        |

| 2.7.7 Solarzelle.....                                           | 64        |

| 2.7.8 Lumineszenzdiode .....                                    | 67        |

| 2.8 Dioden-Grundschaltungen.....                                | 71        |

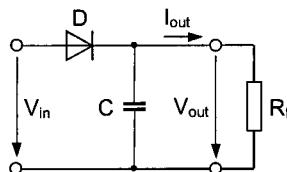

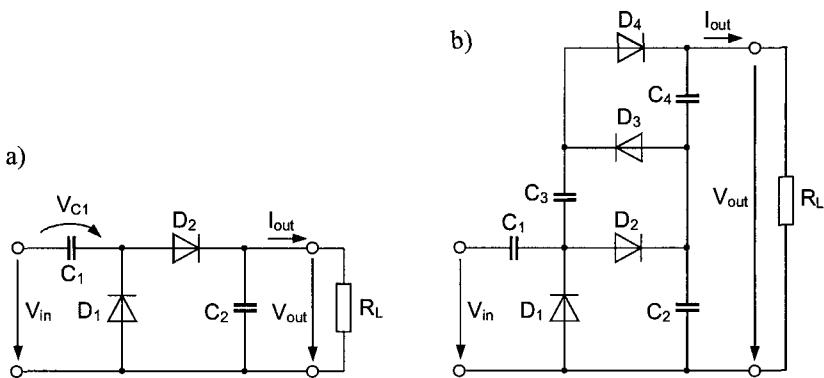

| 2.8.1 Einweggleichrichter .....                                 | 71        |

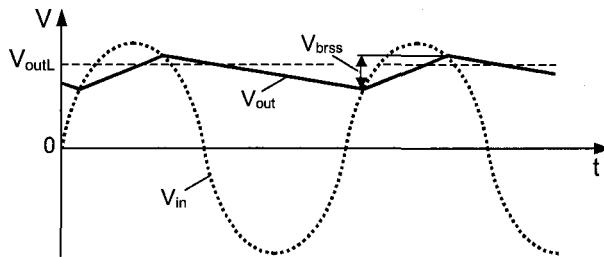

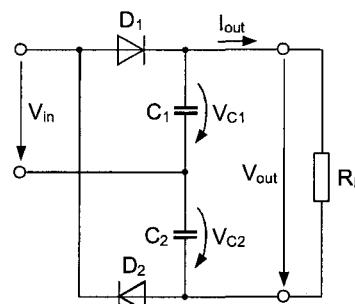

| 2.8.2 Zweiwegbrückenschaltung.....                              | 72        |

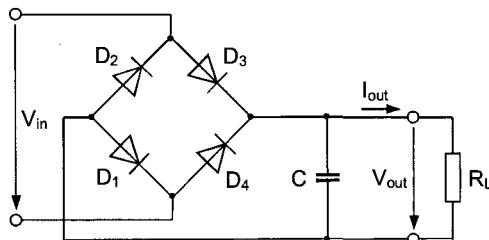

| 2.8.3 Spannungsvervielfacher .....                              | 73        |

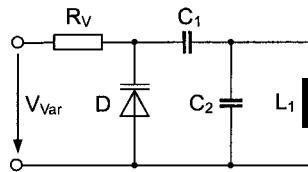

| 2.8.4 Frequenzmodulation .....                                  | 74        |

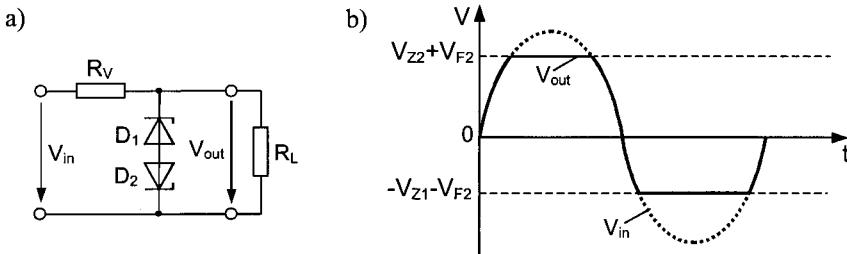

| 2.8.5 Spannungsbegrenzung .....                                 | 75        |

| <b>3 Bipolartransistoren .....</b>                              | <b>77</b> |

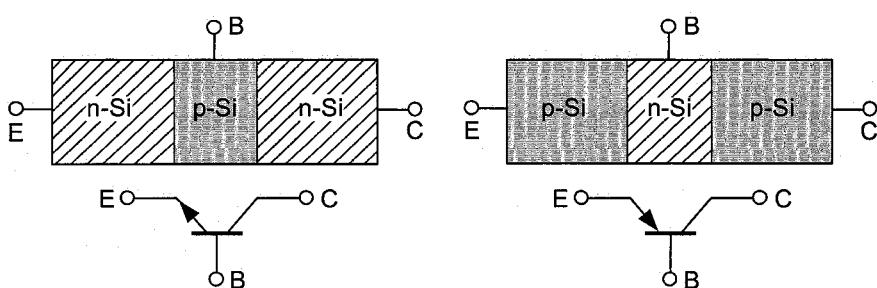

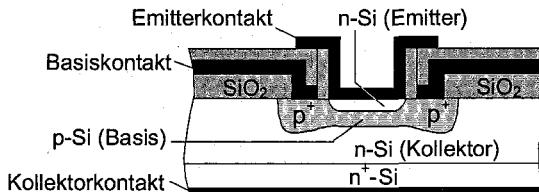

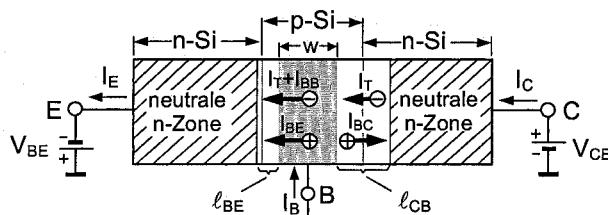

| 3.1 Aufbau und Funktionsweise des Bipolartransistors .....      | 77        |

| 3.1.1 Aufbau des Bipolartransistors.....                        | 77        |

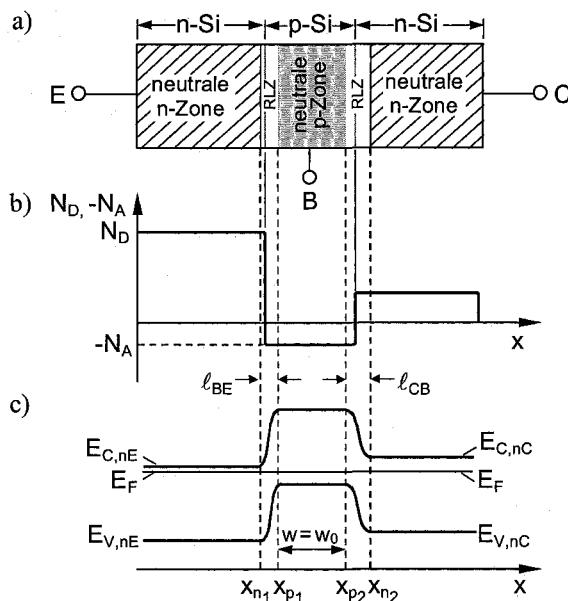

| 3.1.2 Bipolartransistor im thermodynamischen Gleichgewicht..... | 78        |

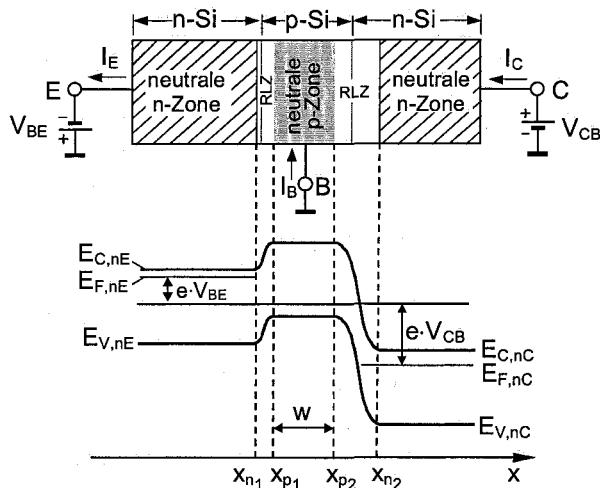

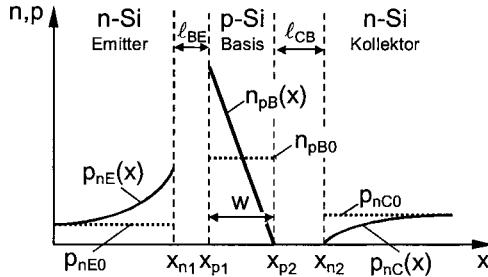

| 3.1.3 Bipolartransistor in Vorwärtsbetrieb.....                 | 79        |

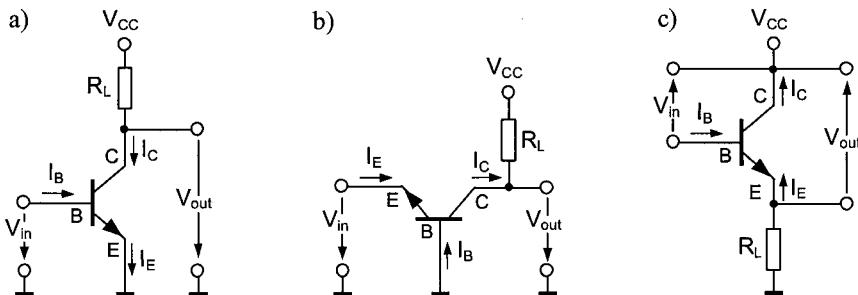

| 3.1.4 Beschaltungsarten .....                                   | 82        |

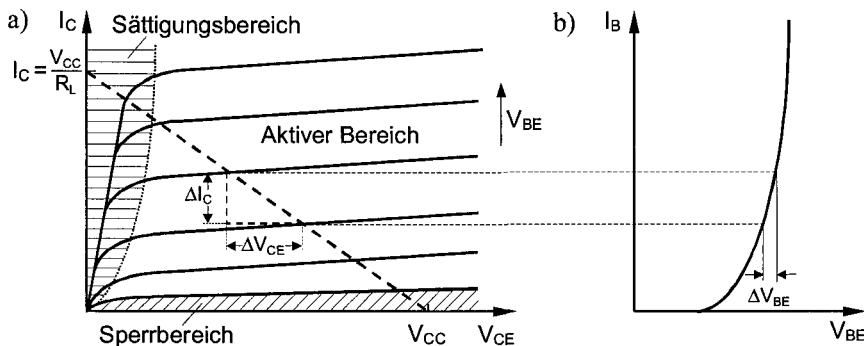

| 3.2 Strom-Spannungs-Charakteristik des Bipolartransistors ..... | 84        |

| 3.2.1 Transistorkennlinie .....                                 | 84        |

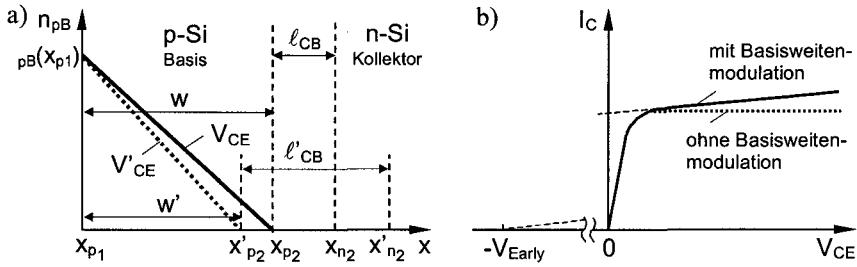

| 3.2.2 Basisweitenmodulation .....                               | 85        |

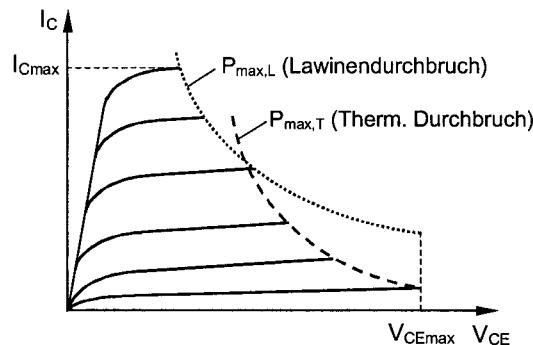

| 3.3 Durchbruchsmechanismen .....                                | 86        |

---

|                                                                   |            |

|-------------------------------------------------------------------|------------|

| 3.3.1 Lawinendurchbruch .....                                     | 86         |

| 3.3.2 Durchbruch zweiter Art (thermischer Durchbruch) .....       | 87         |

| 3.3.3 Punch-Through-Effekt .....                                  | 87         |

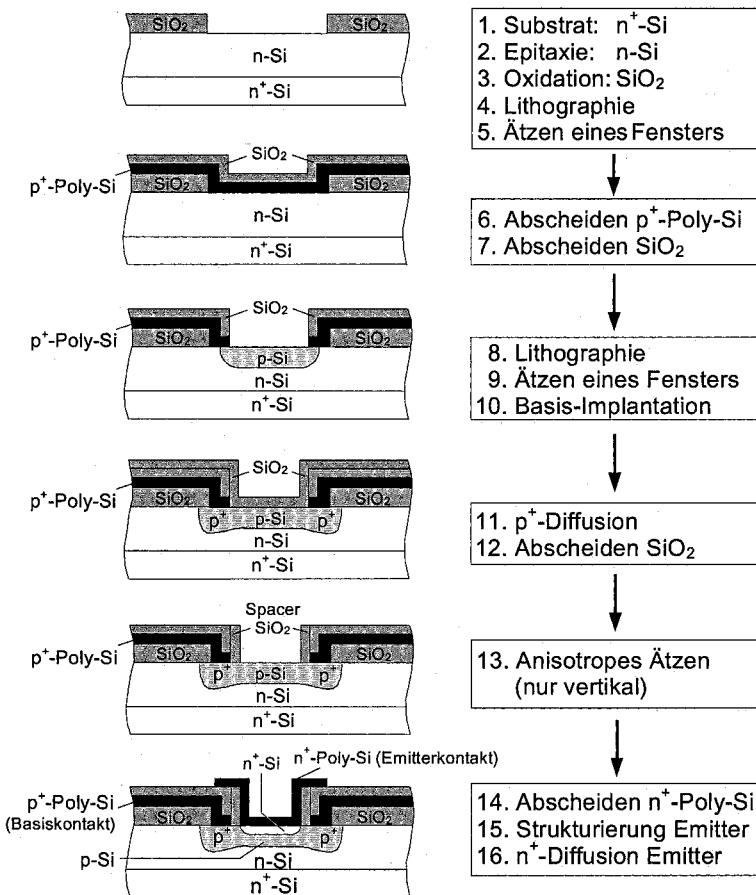

| 3.4 Technologische Realisierung .....                             | 88         |

| 3.5 Netzwerkmodelle des Bipolartransistors .....                  | 89         |

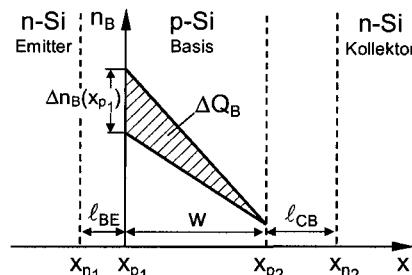

| 3.5.1 Sperrsicht- und Diffusionskapazität .....                   | 89         |

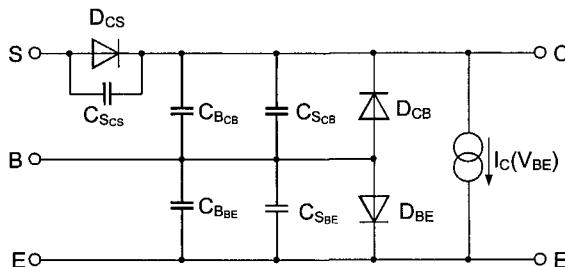

| 3.5.2 Großsignalersatzschaltbild .....                            | 90         |

| 3.5.3 Kleinsignalersatzschaltbild .....                           | 91         |

| 3.5.4 Grenzfrequenzen .....                                       | 93         |

| 3.6 Schaltverhalten des Bipolartransistors .....                  | 94         |

| 3.7 Bipolartransistor-Grundschaltungen .....                      | 97         |

| 3.7.1 Darlington-Schaltung .....                                  | 97         |

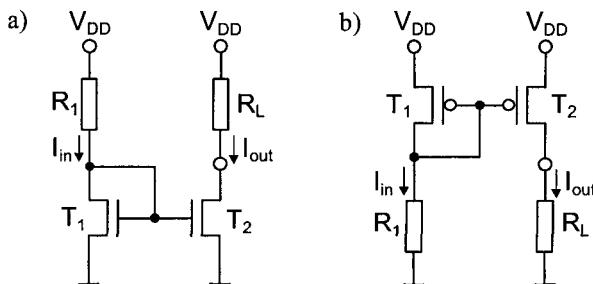

| 3.7.2 Stromquelle und Stromspiegel .....                          | 99         |

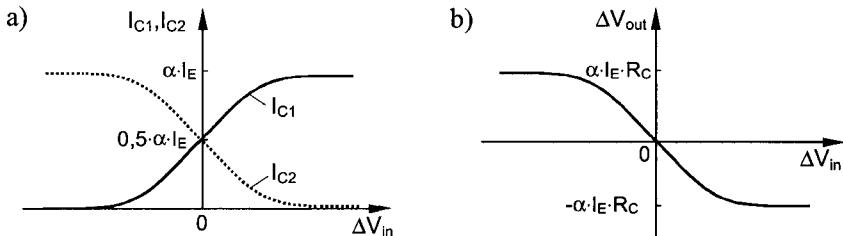

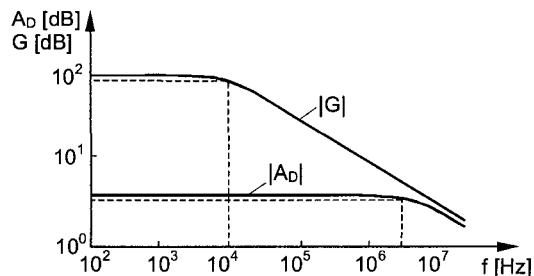

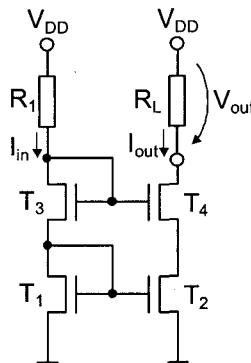

| 3.7.3 Differenzverstärker .....                                   | 102        |

| <b>4 Feldeffekttransistoren .....</b>                             | <b>105</b> |

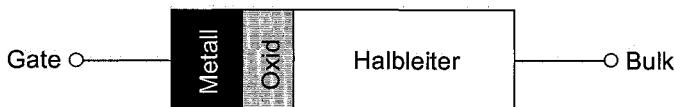

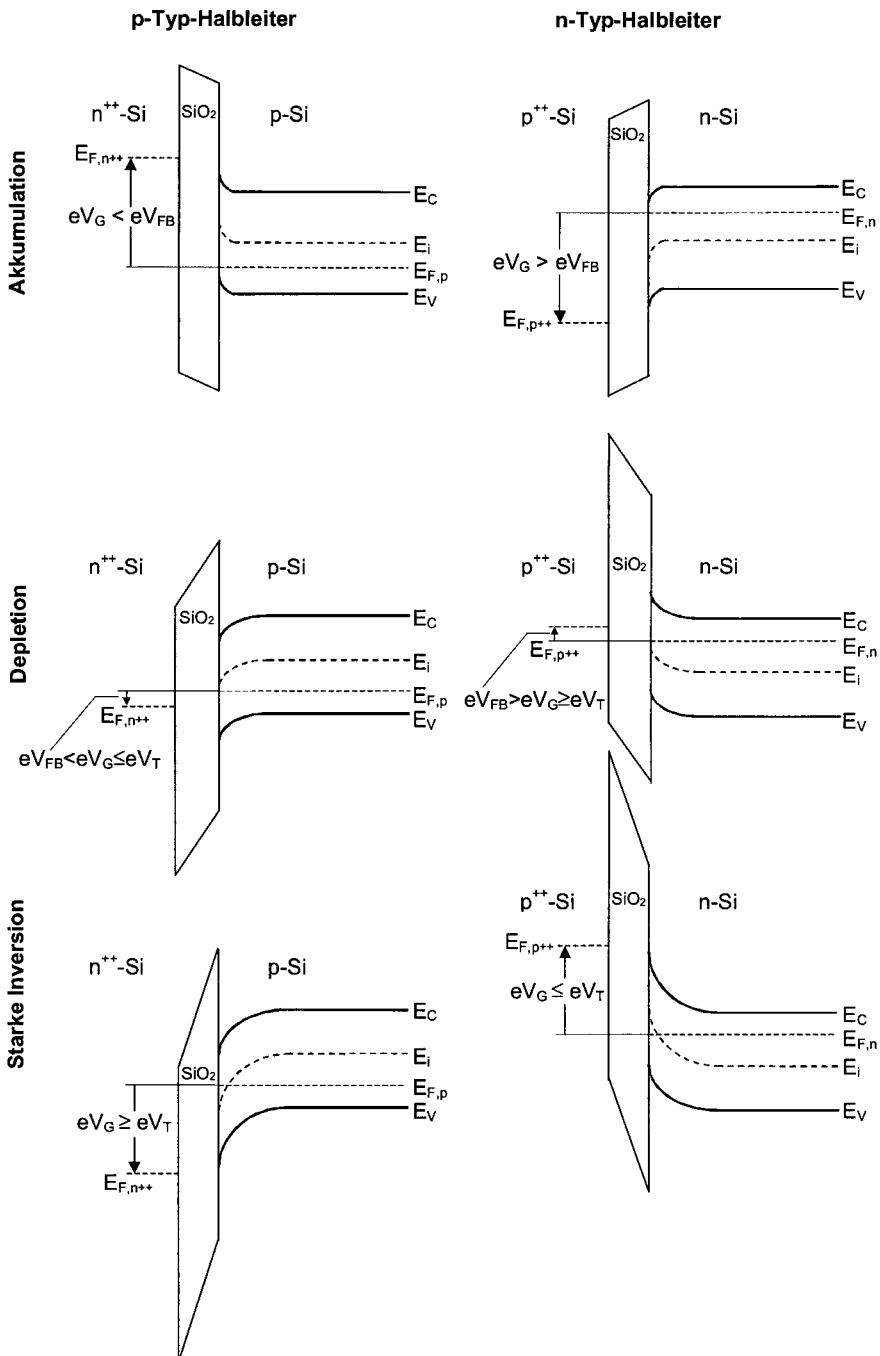

| 4.1 MOS-Struktur .....                                            | 105        |

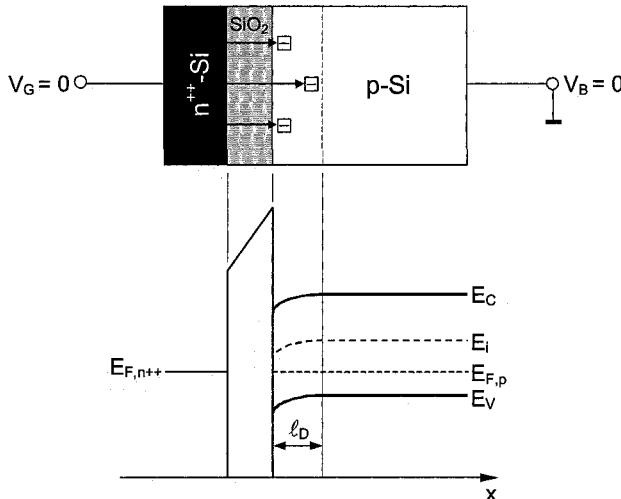

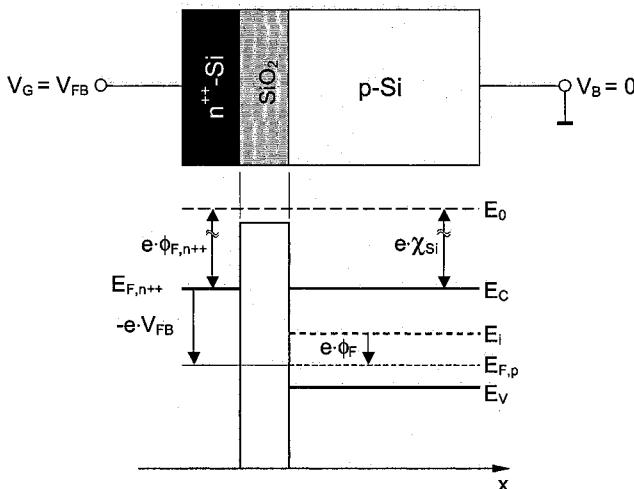

| 4.1.1 MOS-Struktur im thermodynamischen Gleichgewicht .....       | 105        |

| 4.1.2 MOS-Struktur im Flachbandfall .....                         | 106        |

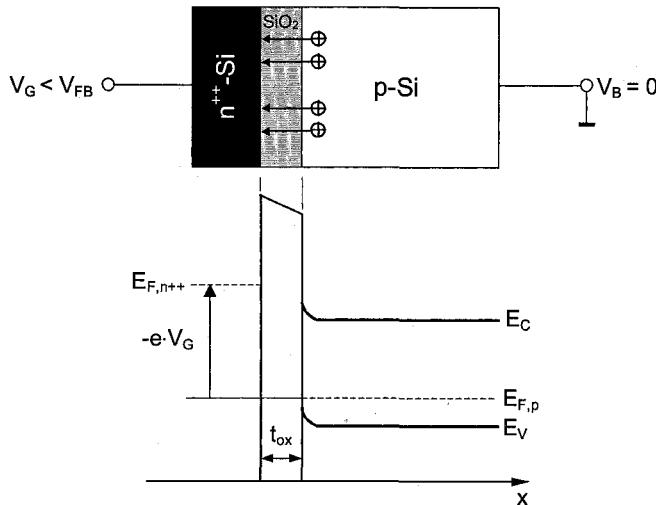

| 4.1.3 MOS-Struktur in Akkumulation .....                          | 107        |

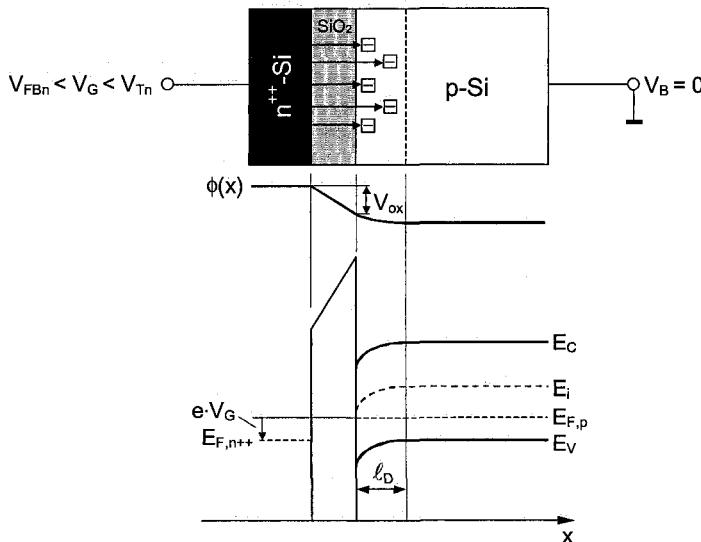

| 4.1.4 MOS-Struktur in Verarmung .....                             | 108        |

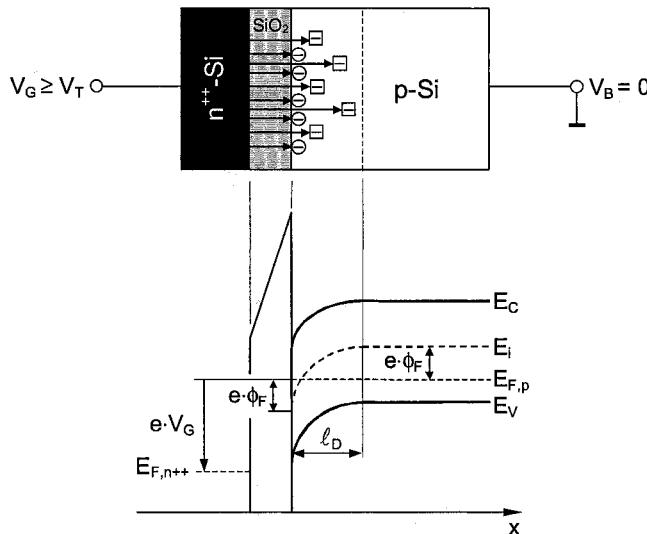

| 4.1.5 MOS-Struktur in Inversion .....                             | 109        |

| 4.1.6 Kapazität der MOS-Struktur .....                            | 111        |

| 4.1.7 Komplementäre MOS-Strukturen .....                          | 113        |

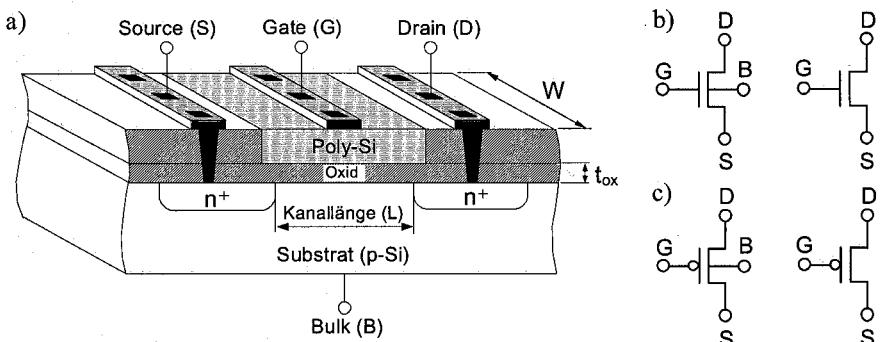

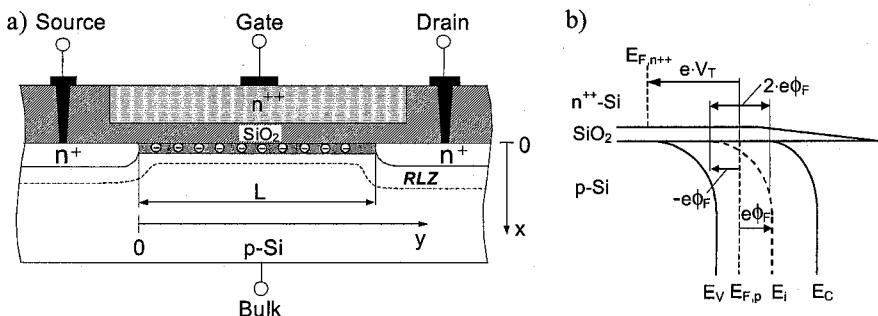

| 4.2 Aufbau und Funktionsweise des MOS-Feldeffekttransistors ..... | 115        |

| 4.2.1 Aufbau des MOSFETs .....                                    | 115        |

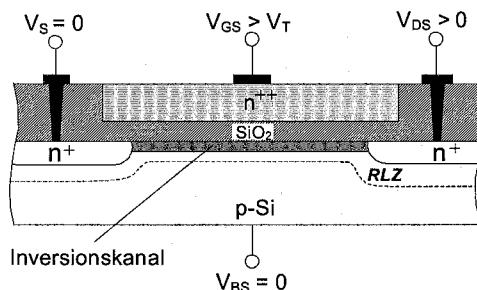

| 4.2.2 Funktionsweise des MOSFETs .....                            | 115        |

| 4.3 Strom-Spannungs-Charakteristik des MOSFETs .....              | 117        |

| 4.3.1 Theorie der Ladungssteuerung .....                          | 117        |

| 4.3.2 Einsatzspannung des MOSFETs .....                           | 120        |

| 4.3.3 Substratsteuerung des MOSFETs .....                         | 121        |

| 4.3.4 Unterschwellstrom des MOSFETs .....                         | 122        |

| 4.3.5 Thermisches Verhalten des MOSFETs .....                     | 122        |

| 4.4 Geometrieabhängigkeit von MOSFET-Parametern .....             | 123        |

| 4.5 Durchbruchsmechanismen und Degradation .....                  | 124        |

| 4.6 Technologische Realisierung .....                             | 126        |

| 4.7 Netzwerkmodelle des MOSFETs .....                             | 127        |

| 4.7.1 MOSFET-Kapazitäten .....                                    | 127        |

| 4.7.2 Großsignalersatzschaltbild .....                            | 128        |

| 4.7.3 Kleinsignalersatzschaltbild .....                           | 129        |

| 4.8 MOSFET-Grundschaltungen .....                                 | 130        |

| 4.8.1 Einfache Verstärkerschaltungen .....                        | 130        |

| 4.8.1.1 Source-Schaltung .....                                    | 130        |

| 4.8.1.2 Drain- und Gate-Schaltung .....                           | 132        |

| 4.8.2 CMOS-Inverter .....                                         | 132        |

| 4.8.2.1 Statisches Übertragungsverhalten .....                    | 132        |

|                                                                     |            |

|---------------------------------------------------------------------|------------|

| 4.8.2.2 Schaltverhalten des CMOS-Inverters .....                    | 134        |

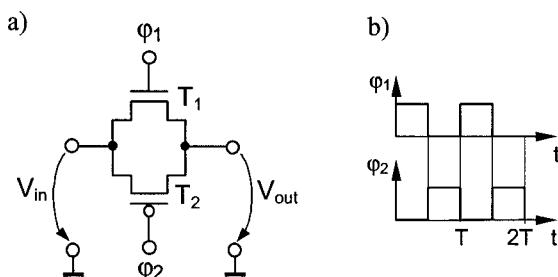

| 4.8.3 Transmissiongate .....                                        | 136        |

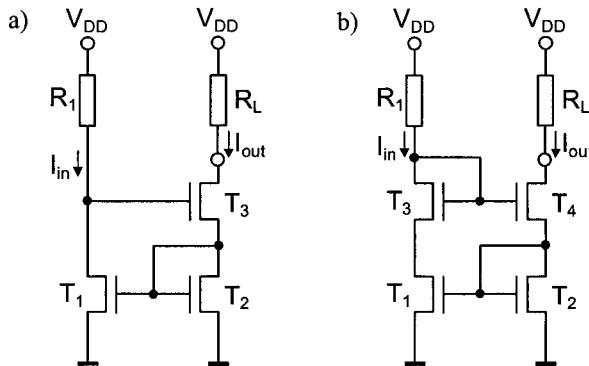

| 4.8.4 Stromspiegel.....                                             | 137        |

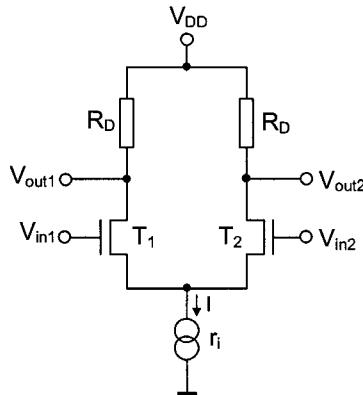

| 4.8.5 Differenzverstärker .....                                     | 140        |

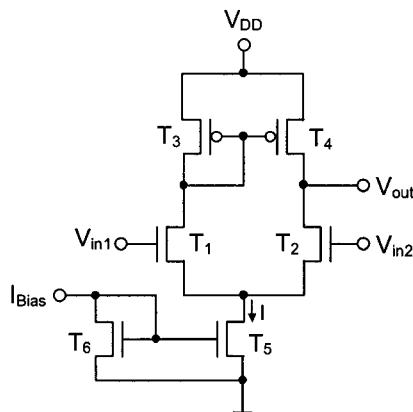

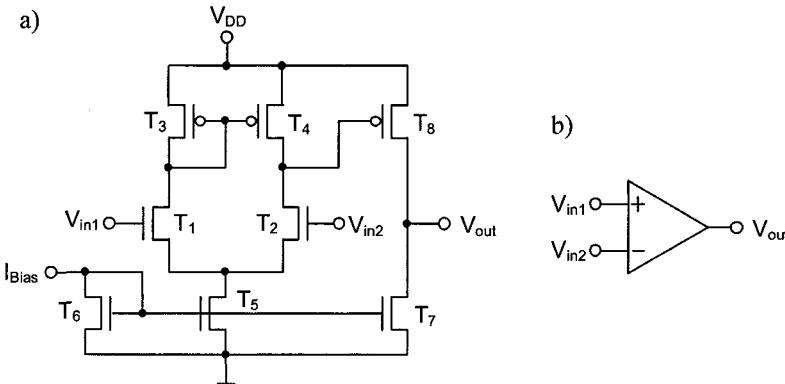

| 4.8.6 Operationsverstärker .....                                    | 141        |

| 4.9 Vergleich von Bipolartransistor und MOSFET .....                | 144        |

| 4.9.1 Technologischer und parametrischer Vergleich.....             | 144        |

| 4.9.2 Einsatzkriterien von Bipolar- und Feldeffekttransistoren..... | 145        |

| <b>5 Leistungsbauelemente .....</b>                                 | <b>146</b> |

| 5.1 psn-Leistungsdiode .....                                        | 146        |

| 5.2 Leistungs bipolartransistor .....                               | 148        |

| 5.3 Leistungs-MOSFET .....                                          | 150        |

| 5.4 Thyristor.....                                                  | 154        |

| 5.4.1 Aufbau und Wirkungsweise des Thyristors.....                  | 154        |

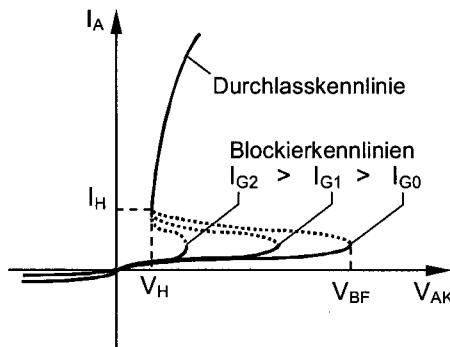

| 5.4.2 Thyristorkennlinie.....                                       | 156        |

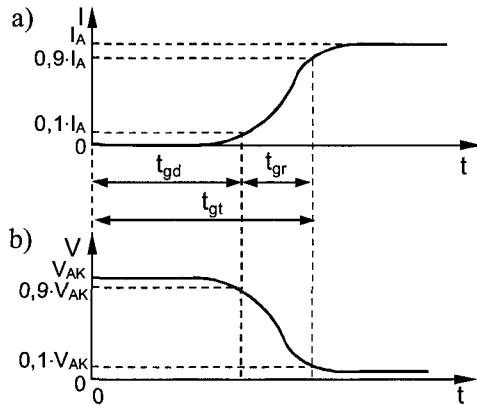

| 5.4.3 Zündverhalten des Thyristors .....                            | 157        |

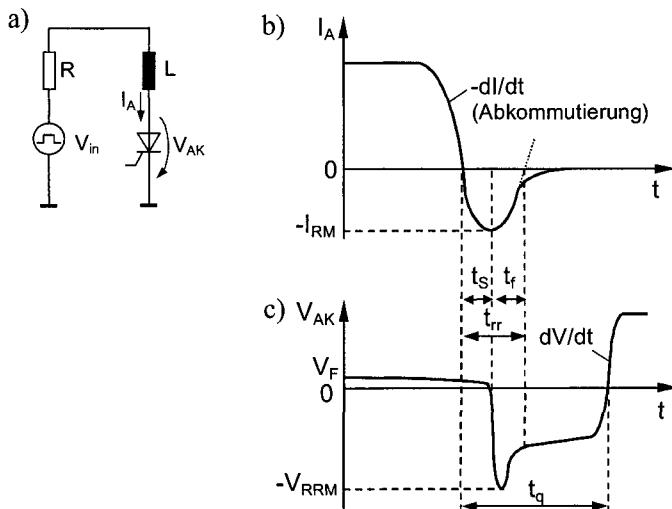

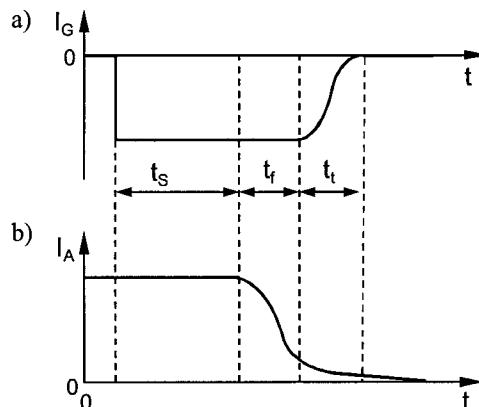

| 5.4.4 Schaltverhalten des Thyristors.....                           | 159        |

| 5.4.5 Weitere Thyristortypen .....                                  | 161        |

| 5.4.5.1 Fotothyristor .....                                         | 161        |

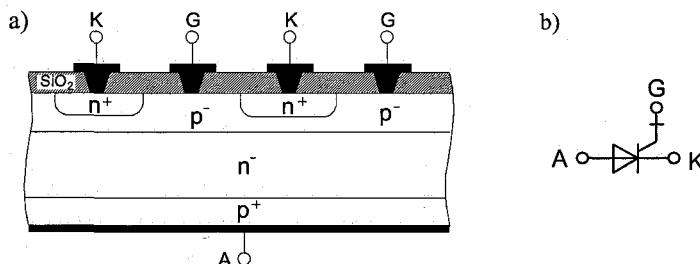

| 5.4.5.2 GTO-Thyristor.....                                          | 161        |

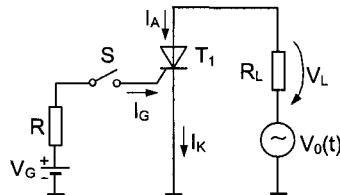

| 5.4.6 Anwendung des Thyristors.....                                 | 162        |

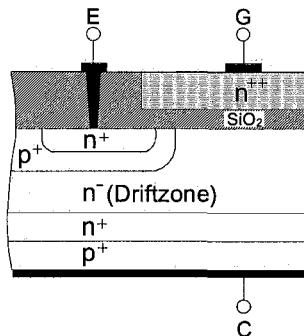

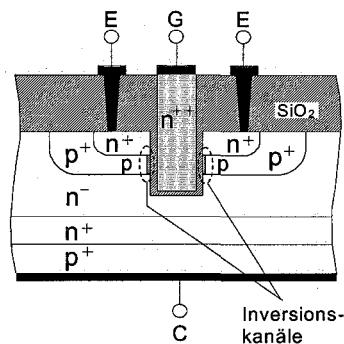

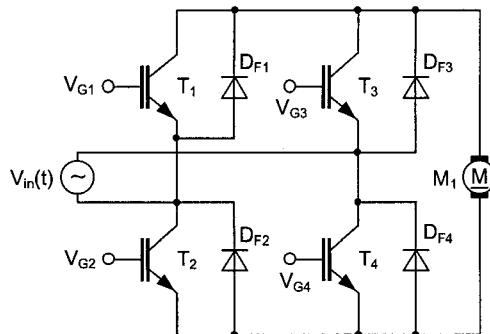

| 5.5 IGBT .....                                                      | 164        |

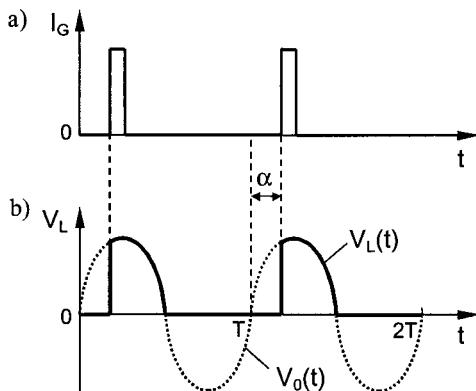

| 5.5.1 Aufbau und Wirkungsweise des IGBTs .....                      | 164        |

| 5.5.2 Kennlinie des IGBTs.....                                      | 166        |

| 5.5.3 Schaltverhalten des IGBTs .....                               | 166        |

| 5.5.4 Weitere IGBT-Typen .....                                      | 168        |

| 5.5.4.1 Punch-Through-IGBT .....                                    | 168        |

| 5.5.4.2 Trench-IGBT .....                                           | 169        |

| 5.5.5 Anwendung des IGBTs .....                                     | 170        |

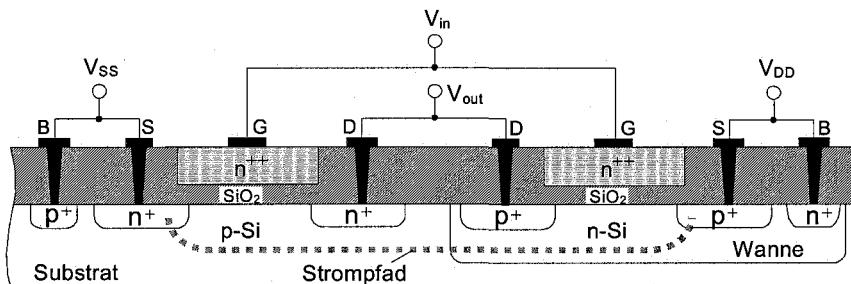

| 5.6 Latch-up-Effekt .....                                           | 170        |

| <b>6 Halbleitersensoren.....</b>                                    | <b>172</b> |

| 6.1 Temperatursensoren.....                                         | 172        |

| 6.1.1 Grenzflächen-Temperatursensoren .....                         | 172        |

| 6.1.2 Spreading-Resistance Si-Temperatursensoren.....               | 174        |

| 6.1.3 Thermopiles.....                                              | 177        |

| 6.2 Magnetosensoren .....                                           | 178        |

| 6.3 Optische Sensoren.....                                          | 182        |

| 6.4 Chemosensoren.....                                              | 187        |

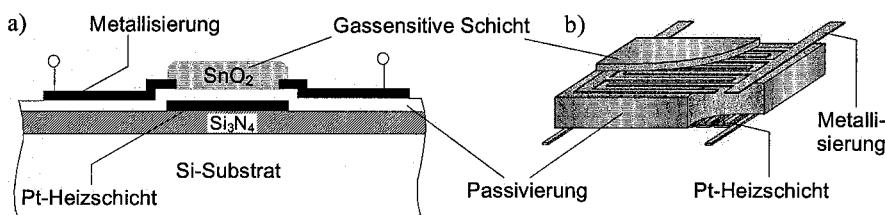

| 6.4.1 Metalloxid-Gassensoren.....                                   | 187        |

| 6.4.2 Chemosensitiver Feldeffekttransistor .....                    | 190        |

| 6.5 Sensoren für mechanische Größen.....                            | 192        |

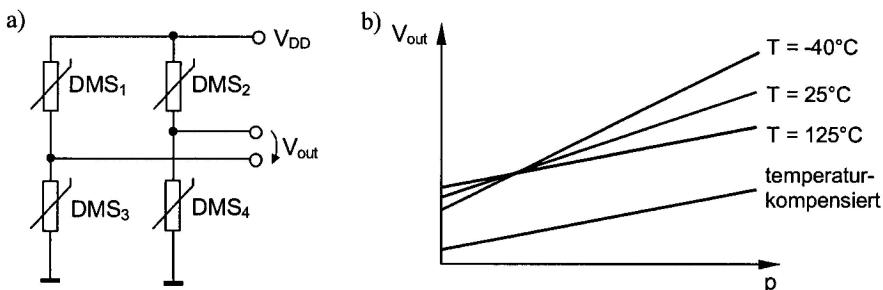

| 6.5.1 Piezoresistive Kraft- und Drucksensoren .....                 | 193        |

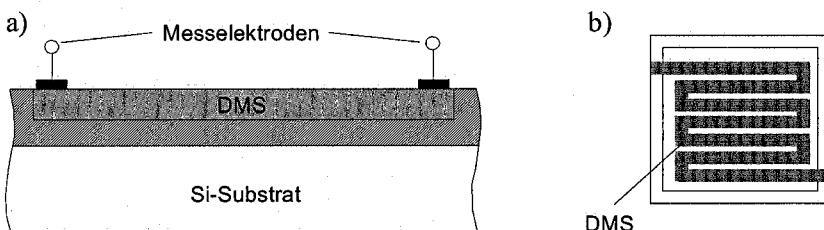

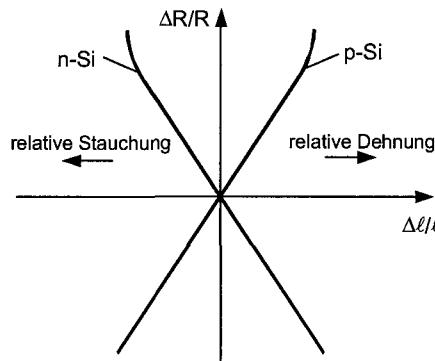

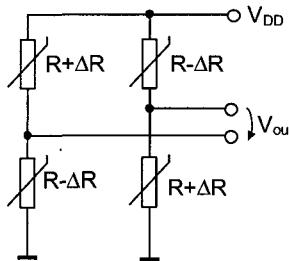

| 6.5.1.1 Halbleiter-Dehnungsmessstreifen .....                       | 193        |

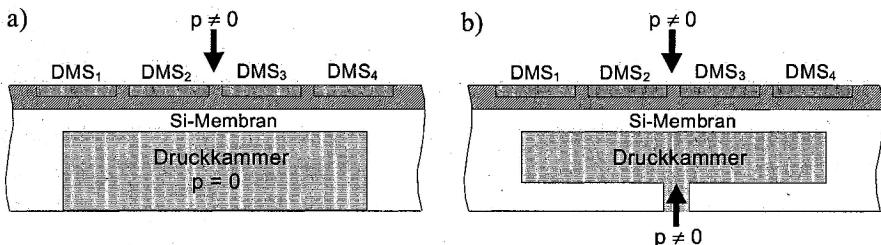

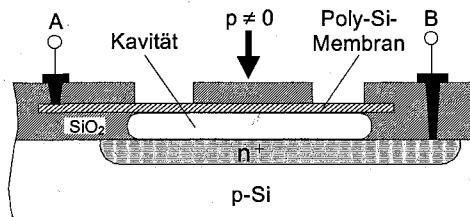

| 6.5.1.2 Piezoresistiver Drucksensor.....                            | 195        |

---

|                                                    |            |

|----------------------------------------------------|------------|

| 6.5.2 Kapazitiver Drucksensor .....                | 196        |

| <b>7 Integrierte Schaltungen .....</b>             | <b>197</b> |

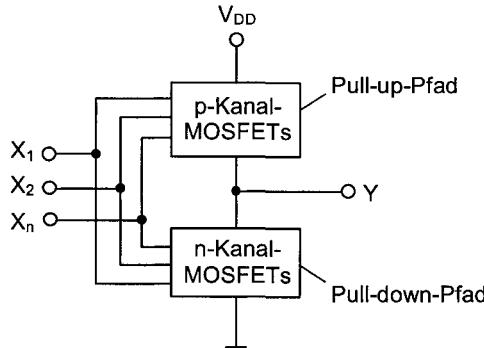

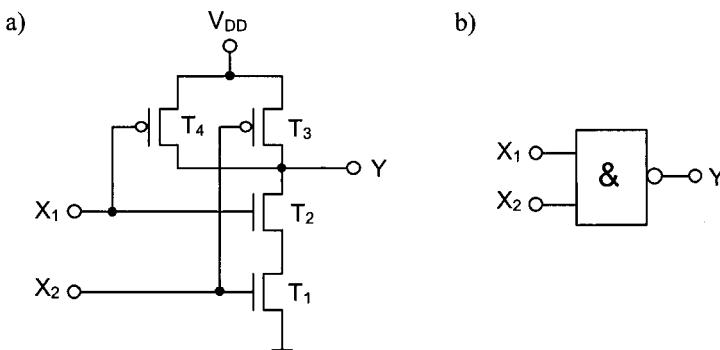

| 7.1 CMOS-Grundschaltungen .....                    | 197        |

| 7.1.1 Statische CMOS-Logik .....                   | 197        |

| 7.1.1.1 Realisierung logischer Verknüpfungen ..... | 197        |

| 7.1.1.2 Tristate-Treiber .....                     | 201        |

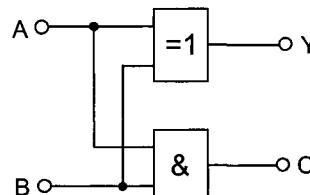

| 7.1.1.3 Addierer .....                             | 202        |

| 7.1.2 Dynamische CMOS-Logik .....                  | 204        |

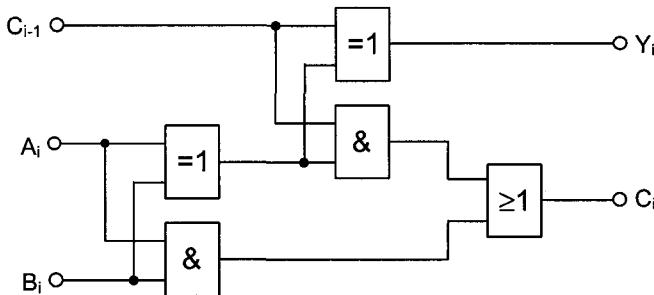

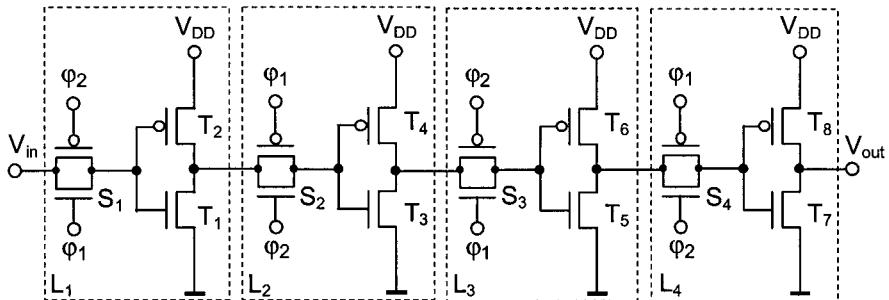

| 7.1.2.1 Dynamisches Latch .....                    | 204        |

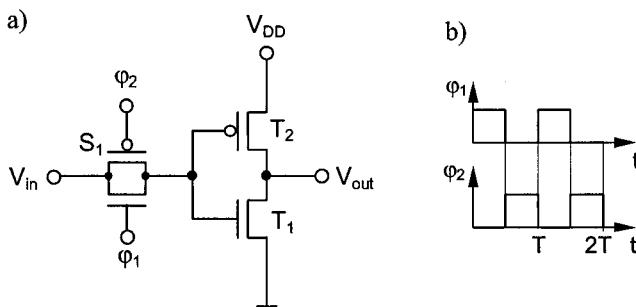

| 7.1.2.2 Dynamisches Schieberegister .....          | 204        |

| 7.2 Speicher .....                                 | 205        |

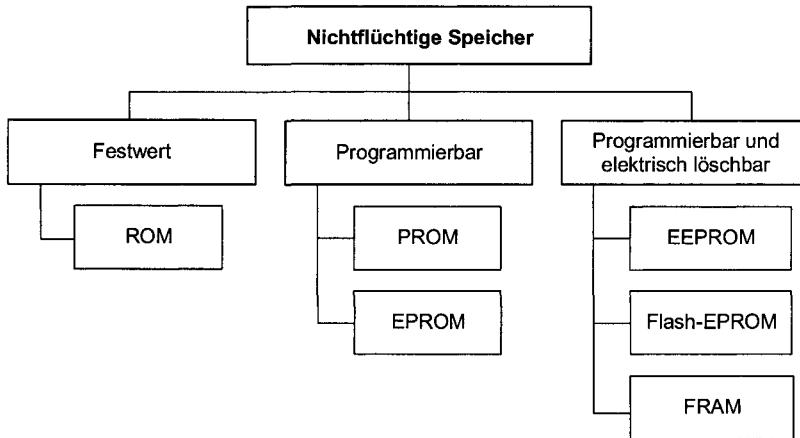

| 7.2.1 Nichtflüchtige Speicher .....                | 205        |

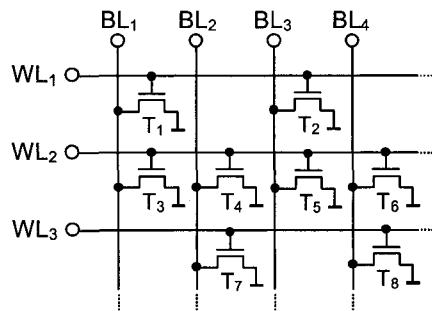

| 7.2.1.1 ROM .....                                  | 206        |

| 7.2.1.2 PROM .....                                 | 207        |

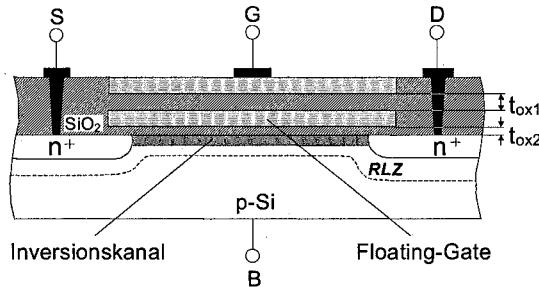

| 7.2.1.3 EPROM .....                                | 207        |

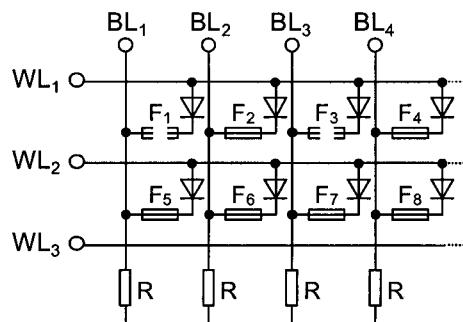

| 7.2.1.4 EEPROM .....                               | 209        |

| 7.2.1.5 Flash-EPROM .....                          | 211        |

| 7.2.1.6 FRAM .....                                 | 211        |

| 7.2.2 Flüchtige Speicher .....                     | 213        |

| 7.2.2.1 SRAM .....                                 | 213        |

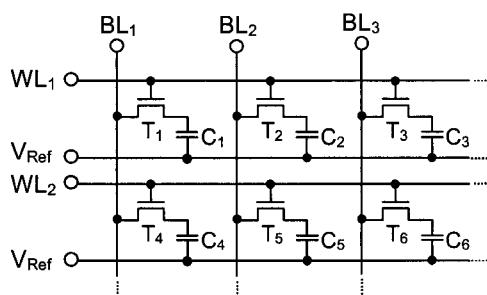

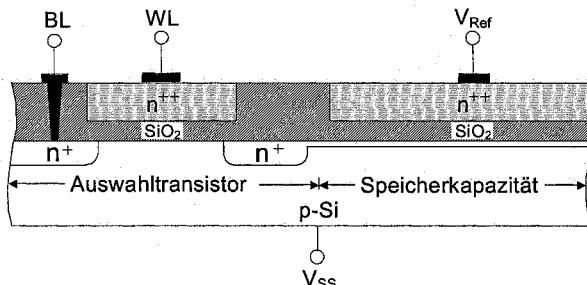

| 7.2.2.2 DRAM .....                                 | 214        |

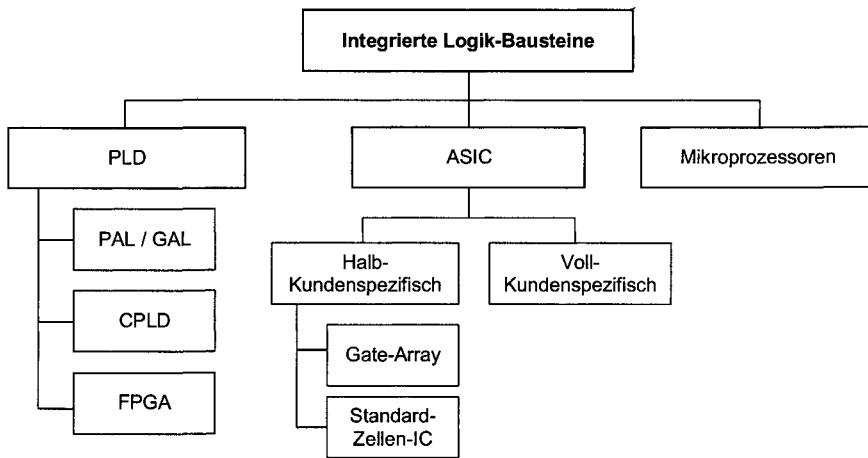

| 7.3 Integrierte Logik-Bausteine .....              | 216        |

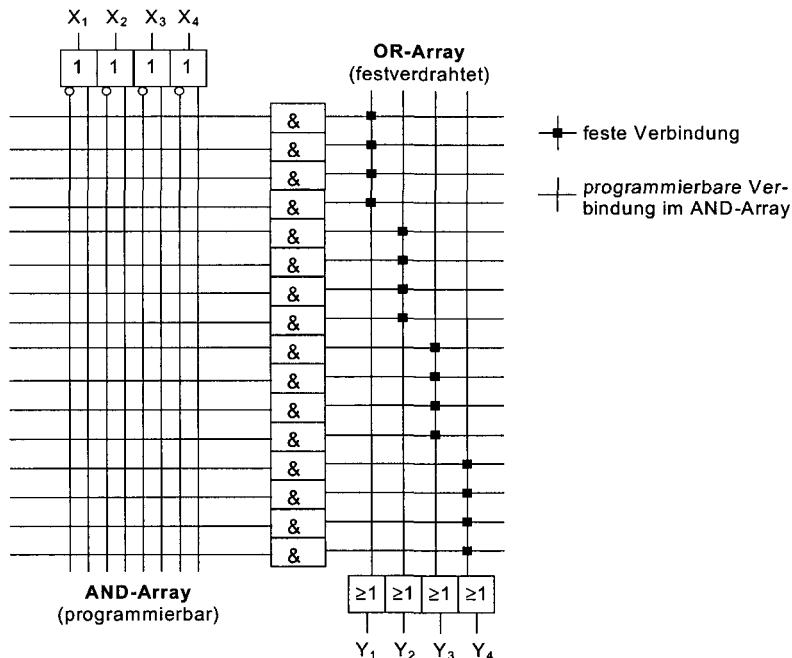

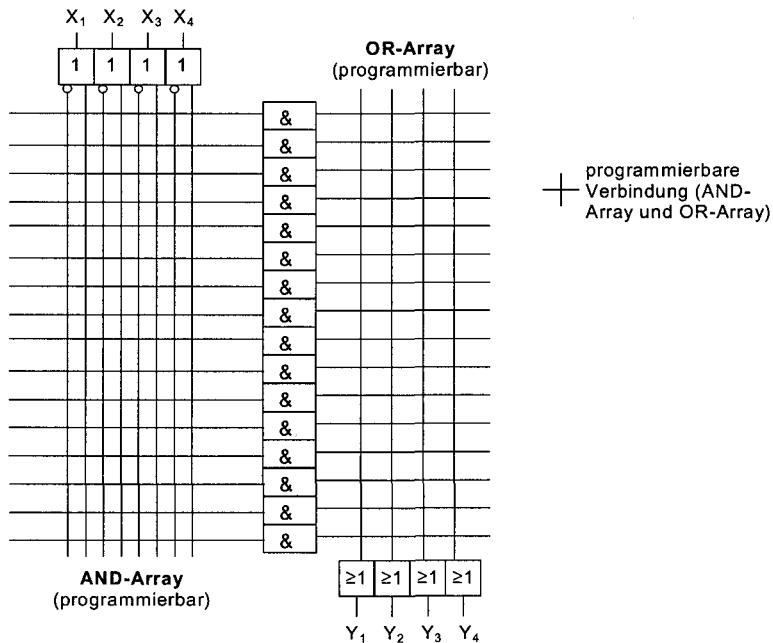

| 7.3.1 PLD .....                                    | 216        |

| 7.3.1.1 PAL und GAL .....                          | 217        |

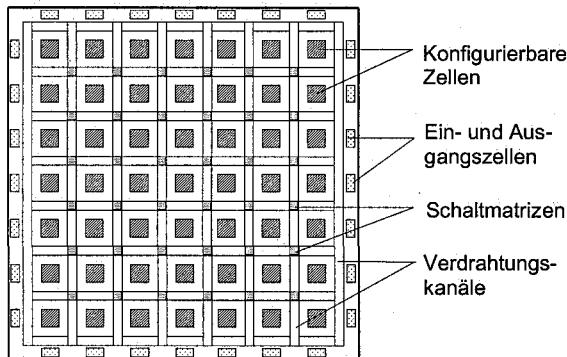

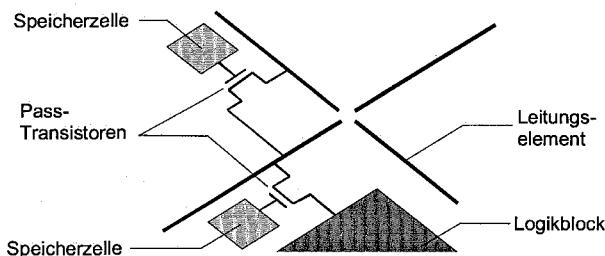

| 7.3.1.2 CPLD .....                                 | 218        |

| 7.3.1.3 FPGA .....                                 | 218        |

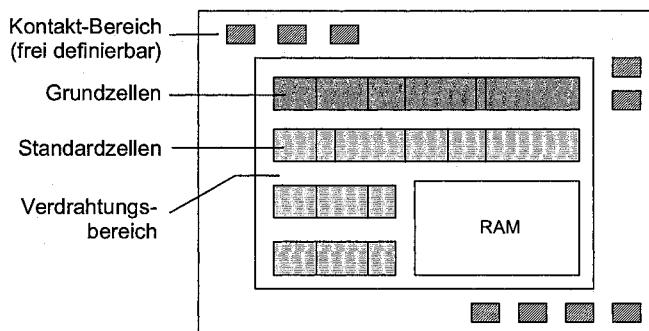

| 7.3.2 ASIC .....                                   | 220        |

| 7.3.2.1 Gate-Array .....                           | 220        |

| 7.3.2.2 Standardzellen-IC .....                    | 220        |

| 7.3.2.3 Voll-kundenspezifischer IC .....           | 221        |

| <b>Literaturverzeichnis .....</b>                  | <b>222</b> |

| <b>Sachverzeichnis .....</b>                       | <b>227</b> |

# Formelzeichen und Naturkonstanten

| Größe        | Bedeutung                                                               | Einheit                                   |

|--------------|-------------------------------------------------------------------------|-------------------------------------------|

| $A$          | Fläche                                                                  | $\text{m}^2$                              |

| $A_D$        | Differenzverstärkung                                                    | —                                         |

| $A_G$        | Gleichtaktverstärkung                                                   | —                                         |

| $A_G$        | Gatefläche                                                              | $\text{m}^2$                              |

| $A_{IB}$     | Stromverstärkung in Basisschaltung                                      | —                                         |

| $A_{IC}$     | Stromverstärkung in Kollektorschaltung                                  | —                                         |

| $A_{IE}$     | Stromverstärkung in Emitterschaltung                                    | —                                         |

| $A_{pn}$     | Fläche einer pn-Diode                                                   | $\text{m}^2$                              |

| $A_{V0}$     | Leerlaufverstärkung                                                     | —                                         |

| $A_{VB}$     | Spannungsverstärkung in Basisschaltung                                  | —                                         |

| $A_{VC}$     | Spannungsverstärkung in Kollektorschaltung                              | —                                         |

| $A_{VE}$     | Spannungsverstärkung in Emitterschaltung                                | —                                         |

| $B$          | Magnetische Induktion                                                   | $\text{V}\cdot\text{s}\cdot\text{m}^{-2}$ |

| $c$          | Lichtgeschwindigkeit $c = 2,998 \cdot 10^8 \text{ m}\cdot\text{s}^{-1}$ | $\text{m}\cdot\text{s}^{-1}$              |

| $C_B$        | Basiskapazität                                                          | F                                         |

| $C_D$        | Depletionkapazität                                                      | $\text{F}\cdot\text{m}^{-2}$              |

| $C_{DB}$     | Drain-Bulk-Sperrschichtkapazität                                        | $\text{F}\cdot\text{m}^{-2}$              |

| $C_{Diff}$   | Diffusionskapazität                                                     | $\text{F}\cdot\text{m}^{-2}$              |

| $C_{GB}$     | Gate-Bulk-Kapazität                                                     | $\text{F}\cdot\text{m}^{-2}$              |

| $C_{GB,min}$ | Minimale Gate-Bulk-Kapazität                                            | $\text{F}\cdot\text{m}^{-2}$              |

| $C_{GD}$     | Gate-Drain-Kapazität                                                    | $\text{F}\cdot\text{m}^{-2}$              |

| $C_{GS}$     | Gate-Source-Kapazität                                                   | $\text{F}\cdot\text{m}^{-2}$              |

| $C_L$        | Lastkapazität                                                           | F                                         |

| $C_{ox}$     | Gateoxidkapazität                                                       | $\text{F}\cdot\text{m}^{-2}$              |

| $C_S$        | Sperrschichtkapazität                                                   | $\text{F}\cdot\text{m}^{-2}$              |

| $C_{SB}$     | Source-Bulk-Sperrschichtkapazität                                       | $\text{F}\cdot\text{m}^{-2}$              |

| $d$          | Durchmesser                                                             | m                                         |

| $D_n$        | Diffusionskonstante der Elektronen                                      | $\text{m}^{-2}\cdot\text{s}^{-1}$         |

| $D_p$        | Diffusionskonstante der Löcher                                          | $\text{m}^{-2}\cdot\text{s}^{-1}$         |

| $e$          | Elementarladung $e = 1,602 \cdot 10^{-19} \text{ C}$                    | C                                         |

| $E$          | Elektrische Feldstärke                                                  | $\text{V}\cdot\text{m}^{-1}$              |

| $E$          | Energie                                                                 | eV                                        |

| $E_\lambda$  | Spektrale Bestrahlungsstärke                                            | $\text{W}\cdot\text{m}^{-2}$              |

| $E_\perp$    | Vertikale Feldstärke                                                    | $\text{V}\cdot\text{m}^{-1}$              |

| Größe           | Bedeutung                                          | Einheit                          |

|-----------------|----------------------------------------------------|----------------------------------|

| $E_{\parallel}$ | Laterale Feldstärke                                | V·m <sup>-1</sup>                |

| $E_A$           | Ionisierungsenergie für Akzeptoren, Akzeptorniveau | eV                               |

| $E_C$           | Energieniveau der unteren Leitungsbandkante        | eV                               |

| $E_{C,min}$     | Leitungsbandminimum im $E$ - $k$ -Raum             | eV                               |

| $E_D$           | Ionisierungsenergie für Donatoren, Donatorniveau   | eV                               |

| $E_F$           | Ferminiveau                                        | eV                               |

| $E_G$           | Bandabstand                                        | eV                               |

| $E_{G0}$        | Bandabstand (zu $T = 0$ K extrapoliert)            | eV                               |

| $E_i$           | Eigenleitungs niveau                               | eV                               |

| $E_M$           | Maximale Feldstärke                                | V·m <sup>-1</sup>                |

| $E_{Ph}$        | Photonenenergie                                    | eV                               |

| $E_{Sat}$       | Sättigungsfeldstärke                               | V·m <sup>-1</sup>                |

| $E_V$           | Energieniveau der oberen Valenzbandkante           | eV                               |

| $E_{V,min}$     | Valenzbandmaximum im $E$ - $k$ -Raum               | eV                               |

| $f$             | Frequenz                                           | Hz                               |

| $F$             | Füllfaktor                                         | —                                |

| $f_{\alpha}$    | $\alpha$ -Grenzfrequenz                            | Hz                               |

| $f_{\beta}$     | $\beta$ -Grenzfrequenz                             | Hz                               |

| $f_0$           | Resonanzfrequenz                                   | Hz                               |

| $f_G$           | Grenzfrequenz                                      | Hz                               |

| $f_{in}$        | Eingangssignalfrequenz                             | Hz                               |

| $F_L$           | Lorentzkraft                                       | N                                |

| $f_T$           | Transitfrequenz                                    | Hz                               |

| $G$             | Gleichtaktunterdrückung                            | —                                |

| $G$             | Generationsrate                                    | m <sup>-3</sup> ·s <sup>-1</sup> |

| $g$             | Zusätzliche Generationsrate                        | m <sup>-3</sup> ·s <sup>-1</sup> |

| $g_0$           | Kleinsignalleitwert für $\omega \rightarrow 0$     | $\Omega^{-1}$                    |

| $g_{BE}$        | Eingangsleitwert zwischen Basis und Emitter        | $\Omega^{-1}$                    |

| $g_{CB}$        | Eingangsleitwert zwischen Kollektor und Basis      | $\Omega^{-1}$                    |

| $g_{DS}$        | Ausgangsleitwert eines MOSFETs                     | $\Omega^{-1}$                    |

| $g_m$           | Steilheit                                          | $\Omega^{-1}$                    |

| $G_T$           | Temperaturleitwert                                 | W·K <sup>-1</sup>                |

| $G_{th}$        | Thermische Generationsrate                         | m <sup>-3</sup> ·s <sup>-1</sup> |

| $\hbar$         | Plancksches Wirkungsquantum                        | J·s                              |

|                 | $\hbar = h/2\pi = 1,054 \cdot 10^{34}$ J·s         |                                  |

| $I$             | Elektrische Stromstärke                            | A                                |

| $i$             | Gesamtkonvektionsstromdichte                       | A·m <sup>-2</sup>                |

| $I_{\lambda}$   | Relative spektrale Intensitätsverteilung           | —                                |

| $I_{2G}$        | Diodenstrom bei 2-Geraden-Näherung                 | A                                |

| $I_A$           | Anodenstrom                                        | A                                |

| $I_B$           | Basisstrom                                         | A                                |

| $I_{BF}$        | Kippstrom                                          | A                                |

| $I_C$           | Kollektorstrom                                     | A                                |

| Größe         | Bedeutung                                                                            | Einheit                                              |

|---------------|--------------------------------------------------------------------------------------|------------------------------------------------------|

| $I_D$         | Drainstrom                                                                           | A                                                    |

| $I_D$         | Strom am pn-Übergang nach Diffusionsmodell                                           | A                                                    |

| $I_{DSat}$    | Drain-Sättigungsstrom                                                                | A                                                    |

| $I_{DSub}$    | Unterschwellstrom                                                                    | A                                                    |

| $I_E$         | Emitterstrom                                                                         | A                                                    |

| $I_{ES}$      | Transfersättigungsstrom                                                              | A                                                    |

| $I_F$         | Strom in Flusspolung                                                                 | A                                                    |

| $I_G$         | Gatestrom                                                                            | A                                                    |

| $I_H$         | Haltestrom                                                                           | A                                                    |

| $I_{in}$      | Eingangsstrom                                                                        | A                                                    |

| $I_K$         | Kurzschlussstrom                                                                     | A                                                    |

| $I_L$         | Fotostrom                                                                            | A                                                    |

| $i_n$         | Konvektionsstromdichte der Elektronen                                                | $\text{A} \cdot \text{m}^{-2}$                       |

| $i_{n,Diff}$  | Diffusionsstromdichte der Elektronen                                                 | $\text{A} \cdot \text{m}^{-2}$                       |

| $i_{n,Drift}$ | Driftstromdichte der Elektronen                                                      | $\text{A} \cdot \text{m}^{-2}$                       |

| $I_{out}$     | Ausgangsstrom                                                                        | A                                                    |

| $i_p$         | Konvektionsstromdichte der Löcher                                                    | $\text{A} \cdot \text{m}^{-2}$                       |

| $i_{p,Diff}$  | Diffusionsstromdichte der Löcher                                                     | $\text{A} \cdot \text{m}^{-2}$                       |

| $i_{p,Drift}$ | Driftstromdichte der Löcher                                                          | $\text{A} \cdot \text{m}^{-2}$                       |

| $I_R$         | Strom am pn-Übergang nach Rekombinations-/Generationsmodell                          | A                                                    |

| $I_{RM}$      | Maximaler Sperrstrom                                                                 | A                                                    |

| $I_S$         | Sperrstrom                                                                           | A                                                    |

| $I_{SD}$      | Sperrsättigungsstrom nach Diffusionsmodell                                           | A                                                    |

| $I_{SR}$      | Sperrsättigungsstrom nach Rekombinations-/Generationsmodell                          | A                                                    |

| $I_T$         | Transferstrom                                                                        | A                                                    |

| $I_V$         | Talwert des Diodenstroms einer Tunneldiode                                           | A                                                    |

| $k$           | k-Faktor von Dehnungsmessstreifen                                                    | —                                                    |

| $k$           | Boltzmann-Konstante $k = 1,380 \cdot 10^{-23} \text{ J} \cdot \text{K}^{-1}$         | $\text{J} \cdot \text{K}^{-1}$                       |

| $k$           | Wellenzahl                                                                           | $\text{m}^{-1}$                                      |

| $K_\lambda$   | Absolute Augenempfindlichkeit                                                        | $\text{lm} \cdot \text{W}^{-1}$                      |

| $k_{B0}$      | Leerlaufempfindlichkeit bei Halleffekt                                               | $\text{m}^2 \cdot \text{A}^{-1} \cdot \text{s}^{-1}$ |

| $k_f$         | Technologieabhängiger Fittingparameter                                               | —                                                    |

| $k_r$         | Technologieabhängiger Fittingparameter                                               | —                                                    |

| $L$           | Induktivität                                                                         | H                                                    |

| $L$           | Kanallänge eines MOSFETs                                                             | m                                                    |

| $L_n$         | Diffusionslänge der Elektronen im p-Typ-Halbleiter                                   | m                                                    |

| $L_p$         | Diffusionslänge der Löcher im n-Typ-Halbleiter                                       | m                                                    |

| $\ell_{BE}$   | Ausdehnung der Raumladungszone zwischen Basis und Emitter eines Bipolartransistors   | m                                                    |

| $\ell_{CB}$   | Ausdehnung der Raumladungszone zwischen Kollektor und Basis eines Bipolartransistors | m                                                    |

| $\ell_D$      | Länge der Raumladungszone                                                            | m                                                    |

| Größe     | Bedeutung                                                                      | Einheit            |

|-----------|--------------------------------------------------------------------------------|--------------------|

| $\ell_n$  | Ausdehnung der Raumladungszone im n-Typ-Halbleiter                             | m                  |

| $\ell_p$  | Ausdehnung der Raumladungszone im p-Typ-Halbleiter                             | m                  |

| $m_n$     | Effektive Masse der Elektronen                                                 | kg                 |

| $m_p$     | Effektive Masse der Löcher                                                     | kg                 |

| $N$       | Nettodotierungsdichte                                                          | $m^{-3}$           |

| $n$       | Ladungsträgerdichte der Elektronen                                             | $m^{-3}$           |

| $n'$      | Überschussträgerdichte der Elektronen                                          | $m^{-3}$           |

| $n_0$     | Ladungsträgerdichte der Elektronen bei thermodynamischem Gleichgewicht         | $m^{-3}$           |

| $N_A$     | Akzeptordotierungsdichte                                                       | $m^{-3}$           |

| $N_A^-$   | Dichte ionisierter Akzeptoren                                                  | $m^{-3}$           |

| $N_C$     | Effektive Zustandsdichte der Leitungsbandkante                                 | $m^{-3}$           |

| $N_D$     | Donatordotierungsdichte                                                        | $m^{-3}$           |

| $N_D^+$   | Dichte ionisierter Donatoren                                                   | $m^{-3}$           |

| $n_E$     | Ladungsträgerverteilung der Elektronen                                         | $J^1 \cdot m^{-3}$ |

| $n_i$     | Eigenleitungsträgerdichte (Si) $n_i = 1,5 \cdot 10^{10} \text{ cm}^{-3}$       | $m^{-3}$           |

| $N_n$     | Zustandsdichte der Elektronen                                                  | $m^{-3}$           |

| $n_{n0}$  | Majoritätsträgerdichte im n-Typ-Halbleiter bei thermodynamischem Gleichgewicht | $m^{-3}$           |

| $N_p$     | Zustandsdichte der Löcher                                                      | $m^{-3}$           |

| $n_{p0}$  | Minoritätsträgerdichte im p-Typ-Halbleiter bei thermodynamischem Gleichgewicht | $m^{-3}$           |

| $n_S$     | Elektronendichte an der Grenzfläche Halbleiter/Oxid                            | $m^{-3}$           |

| $N_V$     | Effektive Zustandsdichte der Valenzbandkante                                   | $m^{-3}$           |

| $p$       | Druck                                                                          | Pa                 |

| $p$       | Ladungsträgerdichte der Löcher                                                 | $m^{-3}$           |

| $p'$      | Überschussträgerdichte der Löcher                                              | $m^{-3}$           |

| $p_0$     | Ladungsträgerdichte der Löcher bei thermodynamischem Gleichgewicht             | $m^{-3}$           |

| $p_E$     | Ladungsträgerverteilung der Löcher                                             | $J^1 \cdot m^{-3}$ |

| $P_{el}$  | Elektrische Leistung                                                           | W                  |

| $P_L$     | Lichtleistung                                                                  | W                  |

| $p_{n0}$  | Minoritätsträgerdichte im n-Typ-Halbleiter bei thermodynamischem Gleichgewicht | $m^{-3}$           |

| $p_{p0}$  | Majoritätsträgerdichte im p-Typ-Halbleiter bei thermodynamischem Gleichgewicht | $m^{-3}$           |

| $p_S$     | Löcherdichte an der Grenzfläche Halbleiter/Oxid                                | $m^{-3}$           |

| $P_V$     | Verlustleistung                                                                | W                  |

| $Q$       | Ladung                                                                         | C                  |

| $Q_{Akk}$ | Flächenladungsdichte in Akkumulation                                           | $C \cdot m^{-2}$   |

| $Q_B$     | Basisladung                                                                    | C                  |

| $Q_D$     | Flächenladungsdichte in Depletion                                              | $C \cdot m^{-2}$   |

| Größe       | Bedeutung                                                                             | Einheit                             |

|-------------|---------------------------------------------------------------------------------------|-------------------------------------|

| $Q_G$       | Gateladung                                                                            | C                                   |

| $Q_I$       | Flächenladungsdichte in Inversion                                                     | $\text{C} \cdot \text{m}^{-2}$      |

| $Q_{SS}$    | Oberflächenladungsdichte                                                              | $\text{C} \cdot \text{m}^{-2}$      |

| $Q_T$       | Tail-Ladung                                                                           | C                                   |

| $R$         | Elektrischer Widerstand                                                               | $\Omega$                            |

| $R$         | Rekombinationsrate                                                                    | $\text{m}^{-3} \cdot \text{s}^{-1}$ |

| $r$         | Rekombinationskoeffizient                                                             | $\text{m}^3 \cdot \text{s}^{-1}$    |

| $R_B$       | Bahnwiderstand                                                                        | $\Omega$                            |

| $r_B$       | Kleinsignalbahnwiderstand                                                             | $\Omega$                            |

| $r_{CE}$    | Kleinsignalausgangswiderstand (Kollektor-Emitter-Widerstand) eines Bipolartransistors | $\Omega$                            |

| $r_{DS}$    | Kleinsignalausgangswiderstand (Drain-Source-Widerstand) eines MOSFETs                 | $\Omega$                            |

| $R_{HE}$    | Heizwiderstand                                                                        | $\Omega$                            |

| $R_{Hn}$    | Hallkonstante für n-Typ-Halbleiter                                                    | $\text{m}^3 \cdot \text{C}^{-1}$    |

| $R_{Hp}$    | Hallkonstante für p-Typ-Halbleiter                                                    | $\text{m}^3 \cdot \text{C}^{-1}$    |

| $R_i$       | Innenwiderstand                                                                       | $\Omega$                            |

| $r_i$       | Kleinsignalinnennwiderstand                                                           | $\Omega$                            |

| $r_{in}$    | Eingangswiderstand                                                                    | $\Omega$                            |

| $R_L$       | Lastwiderstand                                                                        | $\Omega$                            |

| $R_{netto}$ | Nettorekombinationsrate                                                               | $\text{m}^{-3} \cdot \text{s}^{-1}$ |

| $R_{on}$    | ON-Widerstand                                                                         | $\Omega$                            |

| $r_{out}$   | Ausgangswiderstand                                                                    | $\Omega$                            |

| $R_P$       | Parallelwiderstand                                                                    | $\Omega$                            |

| $R_{rad}$   | Strahlende Rekombinationsrate                                                         | $\text{m}^{-3} \cdot \text{s}^{-1}$ |

| $R_S$       | Sensorwiderstand                                                                      | $\Omega$                            |

| $R_{th}$    | Thermischer Widerstand                                                                | $\text{K} \cdot \text{W}^{-1}$      |

| $S_\lambda$ | Spektrale Empfindlichkeit                                                             | $\text{A} \cdot \text{W}^{-1}$      |

| $t$         | Zeit                                                                                  | s                                   |

| $T$         | Temperatur                                                                            | $\text{K}, \text{ }^\circ\text{C}$  |

| $T$         | Periodendauer                                                                         | s                                   |

| $T_D$       | Taktverzögerung                                                                       | s                                   |

| $t_{don}$   | Einschaltverzögerung                                                                  | s                                   |

| $T_E$       | Eigenerwärmung                                                                        | K                                   |

| $t_f$       | Abfallzeit                                                                            | s                                   |

| $t_{fr}$    | Vorwärtserholzeit                                                                     | s                                   |

| $T_G$       | Maximale Speicherzeit                                                                 | s                                   |

| $t_{gd}$    | Zündverzugszeit des Thyristors                                                        | s                                   |

| $t_{gt}$    | Zündzeit des Thyristors                                                               | s                                   |

| $t_{ox}$    | Dicke des Gateoxids                                                                   | m                                   |

| $t_q$       | Freiwerdezeit des Thyristors                                                          | s                                   |

| $t_r$       | Anstiegszeit                                                                          | s                                   |

| $t_{rr}$    | Rückwärtserholzeit                                                                    | s                                   |

| Größe                 | Bedeutung                                   | Einheit                      |

|-----------------------|---------------------------------------------|------------------------------|

| $t_s$                 | Speicherzeit                                | s                            |

| $V$                   | Elektrische Spannung                        | V                            |

| $V_\vartheta$         | Temperaturspannung                          | V                            |

| $V_0$                 | Leerlaufspannung                            | V                            |

| $V_{AK}$              | Anoden-Katoden-Spannung                     | V                            |

| $V_B$                 | Bulkspannung                                | V                            |

| $V_{BE}$              | Basis-Emitter-Spannung                      | V                            |

| $V_{BF}$              | Kippspannung                                | V                            |

| $V_{Br}$              | Durchbruchspannung                          | V                            |

| $V_{brss}$            | Brummspannung                               | V                            |

| $V_{BS}$              | Bulk-Source-Spannung                        | V                            |

| $V_{CB}$              | Kollektor-Basis-Spannung                    | V                            |

| $V_{CC}, V_{DD}, V_B$ | Betriebsspannung                            | V                            |

| $V_{CE}$              | Kollektor-Emitter-Spannung                  | V                            |

| $V_{CESat}$           | Kollektor-Emitter-Sättigungsspannung        | V                            |

| $V_D$                 | Diffusionsspannung                          | V                            |

| $V_{DC}$              | Gleichspannung                              | V                            |

| $V_{DS}$              | Drain-Source-Spannung                       | V                            |

| $V_{DSat}$            | Drain-Source-Sättigungsspannung             | V                            |

| $V_{Early}$           | Early-Spannung                              | V                            |

| $V_F$                 | Flussspannung                               | V                            |

| $V_{FB}$              | Flachbandspannung                           | V                            |

| $V_{FP}$              | Einschaltüberspannung                       | V                            |

| $V_G$                 | Gatespannung                                | V                            |

| $V_G$                 | Gleichspannungsanteil                       | V                            |

| $V_{GB}$              | Gate-Bulk-Spannung                          | V                            |

| $V_{GD}$              | Gate-Drain-Spannung                         | V                            |

| $V_{GE}$              | Gate-Emitter-Spannung                       | V                            |

| $V_{GS}$              | Gate-Source-Spannung                        | V                            |

| $V_H$                 | Haltespannung des Thyristors                | V                            |

| $V_H$                 | Hallspannung                                | V                            |

| $V_{HE}$              | Heizspannung                                | V                            |

| $V_{in}$              | Eingangsspannung                            | V                            |

| $v_k$                 | Mittlere Geschwindigkeit von Ladungsträgern | $\text{m}\cdot\text{s}^{-1}$ |

| $V_{Kanal}$           | Kanalspannung                               | V                            |

| $v_n$                 | Driftgeschwindigkeit der Elektronen         | $\text{m}\cdot\text{s}^{-1}$ |

| $v_p$                 | Driftgeschwindigkeit der Löcher             | $\text{m}\cdot\text{s}^{-1}$ |

| $V_{off}$             | Offset-Spannung                             | V                            |

| $V_{out}$             | Ausgangsspannung                            | V                            |

| $V_R$                 | Sperrspannung                               | V                            |

| $V_{RM}$              | Maximale Sperrspannung                      | V                            |

| $V_{RRM}$             | Rückschlagspannung                          | V                            |

| $V_S$                 | Schwellspannung                             | V                            |

| $v_{Sat}$             | Geschwindigkeitssättigung                   | $\text{m}\cdot\text{s}^{-1}$ |

| Größe                | Bedeutung                                                                  | Einheit          |

|----------------------|----------------------------------------------------------------------------|------------------|

| $V_{SS}$             | Massepotential                                                             | V                |

| $V_T$                | Einsatzspannung MOSFET                                                     | V                |

| $V_{Tn}$             | Einsatzspannung n-Kanal-MOSFET                                             | V                |

| $V_{Tn0}$            | Einsatzspannung n-Kanal-MOSFET bei $V_{BS} = 0$                            | V                |

| $V_{Tp}$             | Einsatzspannung p-Kanal-MOSFET                                             | V                |

| $V_{Tp0}$            | Einsatzspannung p-Kanal-MOSFET bei $V_{BS} = 0$                            | V                |

| $V_Z$                | Zenerspannung                                                              | V                |

| $w$                  | Basisweite                                                                 | m                |

| $W$                  | Kanalweite eines MOSFETs                                                   | m                |

| $W$                  | Besetzungswahrscheinlichkeit                                               | –                |

| $w_0$                | Neutrale Basisweite                                                        | m                |

| $x, y, z$            | Ortskoordinaten                                                            | m                |

| $X_G$                | Gaskonzentration                                                           | ppm              |

| $x_J$                | Tiefe des Source- und Draingebiets von MOSFETs                             | m                |

| $x_m$                | Ort des metallurgischen Übergangs                                          | m                |

| $\alpha$             | Differentieller Thermokoeffizient                                          | $V \cdot K^{-1}$ |

| $\alpha$             | Kleinsignalstromverstärkung in Basisschaltung                              | –                |

| $\alpha_0$           | Kleinsignalstromverstärkung in Basisschaltung für $\omega \rightarrow 0$   | –                |

| $\alpha_A, \alpha_B$ | Thermokoeffizienten der Materialien A und B                                | $V \cdot K^{-1}$ |

| $\alpha_{AB}$        | Seebeck-Koeffizient                                                        | $V \cdot K^{-1}$ |

| $\alpha_n$           | Ionisationskoeffizient für Elektronen                                      | $m^{-1}$         |

| $\alpha_p$           | Ionisationskoeffizient für Löcher                                          | $m^{-1}$         |

| $\beta$              | Kleinsignalstromverstärkung in Emitterschaltung                            | –                |

| $\beta_0$            | Kleinsignalstromverstärkung in Emitterschaltung für $\omega \rightarrow 0$ | –                |

| $\chi_{HL}$          | Elektronenaffinität im Halbleiter                                          | V                |

| $\delta$             | Hallwinkel                                                                 | °                |

| $\delta$             | Basistransportfaktor                                                       | –                |

| $\epsilon$           | Dielektrizitätskonstante $\epsilon = \epsilon_0 \cdot \epsilon_r$          | $F \cdot m^{-1}$ |

| $\epsilon_0$         | Vakuum-Dielektrizitätskonstante                                            | $F \cdot m^{-1}$ |

|                      | $\epsilon_0 = 8,854 \cdot 10^{-12} F \cdot m^{-1}$                         |                  |

| $\epsilon_{ox}$      | Dielektrizitätszahl von $SiO_2$ $\epsilon_{ox} = 3,9$                      | –                |

| $\epsilon_r$         | Dielektrizitätszahl                                                        | –                |

| $\epsilon_{Si}$      | Dielektrizitätszahl von Silizium $\epsilon_{Si} = 12$                      | –                |

| $\phi$               | Elektrisches Potential                                                     | V                |

| $\phi_F$             | Fermipotential                                                             | V                |

| $\Phi_{Ph}$          | Photonenstrom                                                              | $s^{-1}$         |

| $\phi_s$             | Oberflächenpotential                                                       | V                |

| $\gamma$             | Body-Faktor                                                                | $V^{1/2}$        |

| $\gamma_n$           | Body-Faktor für n-Kanal-MOSFET                                             | $V^{1/2}$        |

| $\gamma_p$           | Body-Faktor für p-Kanal-MOSFET                                             | $V^{1/2}$        |

| $\eta_Q$             | Quantenwirkungsgrad                                                        | –                |

| Größe        | Bedeutung                                                        | Einheit                         |

|--------------|------------------------------------------------------------------|---------------------------------|

| $\eta_P$     | Programmiereffizient                                             | —                               |

| $\eta_{rad}$ | Quantenausbeute                                                  | —                               |

| $\varphi$    | Taktsignalspannung                                               | V                               |

| $\varphi_R$  | Phasenreserve                                                    | °                               |

| $\varphi_S$  | Phasenverschiebung                                               | °                               |

| $\kappa$     | Absorptionsgrad                                                  | $m^{-1}$                        |

| $\lambda$    | Kanallängenmodulationsfaktor                                     | —                               |

| $\lambda$    | Lichtwellenlänge                                                 | m                               |

| $\mu_{eff}$  | Effektive Beweglichkeit von Ladungsträgern                       | $m^2 \cdot V^{-1} \cdot s^{-1}$ |

| $\mu_H$      | Hallbeweglichkeit                                                | $m^2 \cdot V^{-1} \cdot s^{-1}$ |

| $\mu_n$      | Beweglichkeit der Elektronen                                     | $m^2 \cdot V^{-1} \cdot s^{-1}$ |

| $\mu_p$      | Beweglichkeit der Löcher                                         | $m^2 \cdot V^{-1} \cdot s^{-1}$ |

| $\theta$     | Raumwinkel                                                       | sr                              |

| $\rho$       | Raumladungsdichte                                                | $C \cdot m^{-3}$                |

| $\rho$       | Spezifischer Widerstand                                          | $\Omega \cdot cm$               |

| $\rho_n$     | Ladungsdichte der Elektronen                                     | $C \cdot m^{-3}$                |

| $\rho_p$     | Ladungsdichte der Löcher                                         | $C \cdot m^{-3}$                |

| $\sigma$     | Elektrische Leitfähigkeit                                        | $\Omega^{-1} \cdot cm^{-1}$     |

| $\sigma_T$   | Thermische Leitfähigkeit                                         | $W \cdot m^{-1} \cdot K^{-1}$   |

| $\tau_B$     | Basistransitzeit                                                 | s                               |

| $\tau_D$     | Dielektrische Relaxationszeit                                    | s                               |

| $\tau_d$     | Verzögerungszeit                                                 | s                               |

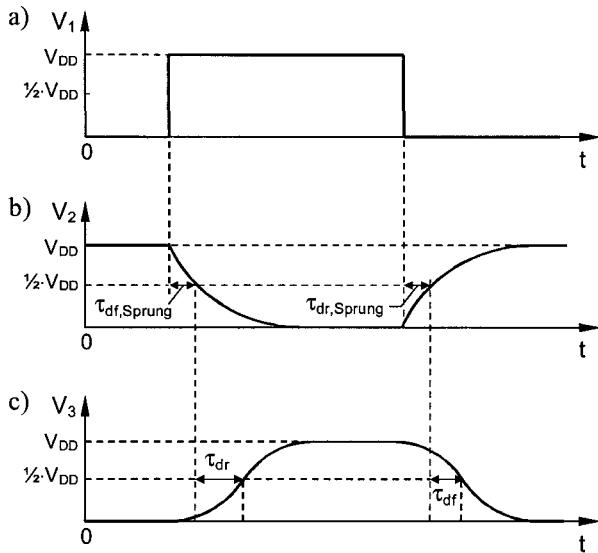

| $\tau_{df}$  | Verzögerungszeit der fallenden Flanke                            | s                               |

| $\tau_{dr}$  | Verzögerungszeit der steigenden Flanke                           | s                               |

| $\tau_n$     | Minoritätsträgerlebensdauer (der Elektronen) im p-Typ-Halbleiter | s                               |

| $\tau_p$     | Minoritätsträgerlebensdauer (der Löcher) im n-Typ-Halbleiter     | s                               |

| $\tau_{RC}$  | RC-Zeitkonstante                                                 | s                               |

| $\tau_S$     | Effektive Ladungsträgerlebensdauer                               | s                               |

| $\tau_{SC}$  | Zeitkonstante von Schaltern                                      | s                               |

| $\tau_T$     | Thermische Zeitkonstante                                         | s                               |

| $\omega$     | Kreisfrequenz                                                    | Hz                              |

# 1 Halbleiter-Grundlagen

Als *Halbleiter* bezeichnet man Materialien, deren spezifischer Widerstand zwischen dem der Leiter (Metalle) und dem der Isolatoren liegt. Der Ladungstransport im Halbleiter stellt die Grundlage für die Funktionsweise der *Halbleiterbauelemente* dar. In diesem Kapitel werden die Eigenschaften von Halbleitern an Hand des *Bindungsmodells* und *Bändermodells* beschrieben. Die Mechanismen des Ladungsträgertransports und das Verhalten des Halbleiters bei Störung des thermodynamischen Gleichgewichts sowie spezielle Halbleitereffekte werden dargestellt. Diese Betrachtungen bilden die Grundlage für das Verständnis der in den nachfolgenden Kapiteln beschriebenen Halbleiterbauelementen und deren schaltungstechnischer Anwendung.

## 1.1 Halbleitermaterialien

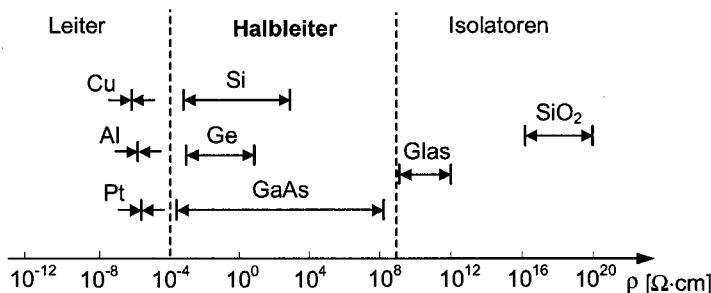

Halbleitermaterialien zeichnen sich insbesondere durch den Wert des spezifischen Widerstandes  $\rho$  bzw. der elektrischen Leitfähigkeit  $\sigma$  aus ( $\rho = 1/\sigma$ ), der bei Raumtemperatur ( $T = 300\text{ K}$ ) zwischen dem der Leiter und dem der Isolatoren liegt ( $10^{-4}\Omega\cdot\text{cm} < \rho < 10^9\Omega\cdot\text{cm}$ ). In Abb. 1.1 ist der spezifische Widerstand  $\rho$  verschiedener Materialien und deren Zuordnung zu Leitern, Halbleitern und Isolatoren dargestellt. Die aufgeführten Materialien sind typische Stoffe, die zur Herstellung von Halbleiterbauelementen verwendet werden.

Abb. 1.1. Spezifischer Widerstand  $\rho$  von typischen Leitern, Halbleitern und Isolatoren bei Raumtemperatur

Im Gegensatz zu Leitern (Metallen), deren spezifischer Widerstand bei Temperaturabnahme absinkt, nimmt bei reinen Halbleitern der spezifische Widerstand

bei Temperaturverringerung zu. Bei einer Temperatur von  $T = 0\text{ K}$  verhalten sich Halbleiter dann hinsichtlich ihrer elektrischen Leitfähigkeit bzw. ihres spezifischen Widerstandes wie Isolatoren.

Die elektrische Leitfähigkeit von Halbleitern kann durch *Dotierung* mit Störstellenatomen variiert und bis in den Bereich der Leiter gesteigert werden. Abhängig von der Dotierungsart (vgl. Abschn. 1.2) existieren im Halbleiter eine sog. *Elektronen-Leitfähigkeit* und eine *Löcher-Leitfähigkeit*, die zusammen die elektrische Leitfähigkeit ergeben. Halbleiter, in denen die Elektronen-Leitfähigkeit dominiert, werden als sog. *n-Typ-Halbleiter* bezeichnet; die Elektronen sind hier die *Majoritätsträger*. Im n-Typ-Halbleiter existiert aber auch eine Löcher-Leitfähigkeit, wobei die Löcher als *Minoritätsträger* bezeichnet werden. Beim *p-Typ-Halbleiter* gilt, dass Löcher die Majoritätsträger und Elektronen die Minoritätsträger sind. Durch Kombination von n-Typ- und p-Typ-Halbleiterschichten können elektronische Bauelemente realisiert werden, bei denen die Wechselwirkungen zwischen Elektronen und Löchern ausgenutzt werden.

Neben der Abhangigkeit der elektrischen Leitfahigkeit von der Dotierung und der Temperatur weisen Halbleiter eine starke Abhangigkeit von elektrischen und magnetischen Feldern sowie von optischen und mechanischen Einflussen auf. Die aus diesen Abhangigkeiten resultierenden Halbleitereffekte werden in entsprechenden Halbleiterbauelementen ausgenutzt, deren wesentliche Ausfuhrungen in diesem Buch beschrieben werden.

Die Halbleitermaterialien werden in sog. *Elementhalbleiter* und *Verbindungs- halbleiter* unterteilt. Elementhalbleiter wie Silizium (Si) und Germanium (Ge) sind aus einem der Elemente der IV. Hauptgruppe des Periodensystems der Elemente (vgl. Abb. 1.2) aufgebaut und weisen eine sog. *Diamantstruktur* auf (vgl. Abschn. 1.2).

| I                  | II                 | III                | IV                 | V                  | VI | VII | VIII              |

|--------------------|--------------------|--------------------|--------------------|--------------------|----|-----|-------------------|

|                    |                    |                    |                    |                    |    |     |                   |

|                    | B<br>5<br>10,82    |                    |                    |                    |    |     | Elementhalbleiter |

|                    | Al<br>13<br>26,97  | Si<br>14<br>28,06  | P<br>15<br>31,02   | S<br>16<br>32,06   |    |     |                   |

| Zn<br>30<br>65,38  | Ga<br>31<br>69,72  | Ge<br>32<br>72,64  | As<br>33<br>74,91  | Se<br>34<br>78,96  |    |     |                   |

| Cd<br>48<br>112,41 | In<br>49<br>114,76 | Sn<br>50<br>118,71 | Sb<br>51<br>121,76 | Te<br>52<br>127,60 |    |     |                   |

**Abb. 1.2.** Auszug aus dem Periodensystem der Elemente mit typischen Stoffen für Elementhalbleiter und Komponenten für Verbindungshalbleiter

Im Gegensatz zu den Elementhalbleitern bestehen Verbindungshalbleiter aus mindestens zwei Elementen. Sie werden entsprechend der Anzahl der beteiligten Komponenten als *binäre*, *ternäre* oder *quaternäre Halbleiter* bezeichnet. Typische binäre Halbleiter sind in der Form  $A^{IV}B^{IV}$  (z. B. SiGe),  $A^{III}B^V$  (z. B. GaAs) oder  $A^{II}B^{VI}$  (z. B. CdSe) aufgebaut, wobei die Elemente A und B der jeweils entsprechenden Hauptgruppe des Periodensystems zu entnehmen sind. Ternäre Halbleiter bestehen aus drei Komponenten (z. B.  $\text{Ga}_{1-x}\text{Al}_x\text{As}$ ) und quaternäre Halbleiter aus

vier Elementen (z. B.  $In_xGa_{1-x}As_yP_{1-y}$ ). Die elektrische Leitfähigkeit von Verbindungshalbleitern kann durch Stöchiometriestörungen oder gezielte Dotierung mit weiteren Komponenten beeinflusst werden. Wird beispielsweise der binäre Verbindungshalbleiter GaAs mit einem Element der II. Hauptgruppe (z. B. Zn) dotiert, so entsteht ein p-Typ-Halbleiter. Wird GaAs hingegen mit einem Element der VI. Hauptgruppe (z. B. Se) dotiert, so entsteht ein n-Typ-Halbleiter.

Auf die technologische Herstellung von Halbleiterstrukturen wird in den Folgekapiteln bei der Betrachtung elektronischer Bauelemente näher eingegangen (vgl. Abschn. 2.4, 3.4, 4.6).

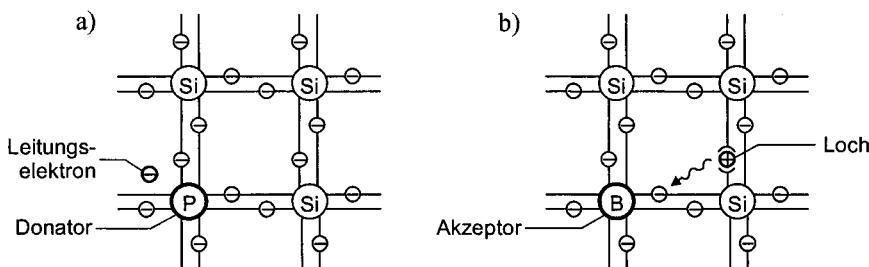

## 1.2 Bindungsmodell

Das Bindungsmodell von Halbleitern beschreibt die grundlegenden Mechanismen, die am Ladungsträgertransport im Halbleiter beteiligt sind. Ausgehend von der Gitterstruktur von Halbleitern wird die im reinen Halbleiter auftretende *Eigenleitung* und die durch Dotierung erzeugte *Störstellenleitung* beschrieben. Die Betrachtungen werden hauptsächlich am Halbleitermaterial Silizium durchgeführt, da Silizium in der Mikroelektronik derzeit die größte Bedeutung besitzt.

### 1.2.1 Gitterstruktur

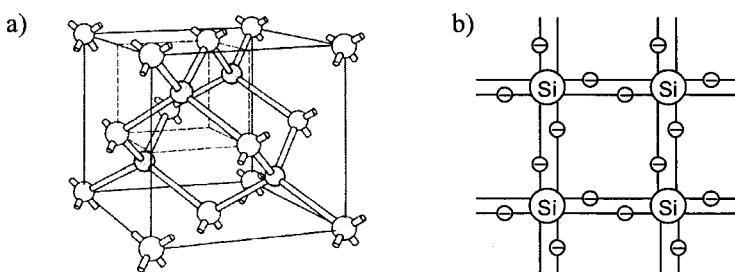

Halbleitermaterialien (vgl. Abschn. 1.1) werden zumeist in *einkristalliner* Form verwendet, die sich durch eine regelmäßige, räumlich wiederkehrende Atomanordnung auszeichnet. Die sich räumlich wiederholenden Grundstrukturen werden *Elementarzellen* genannt. Die chemische Bindung der Atome untereinander wird dabei insbesondere durch die Anzahl der Valenzelektronen der den Atomkern umgebenden Elektronenhülle festgelegt. Ein Silizium-Atom besitzt vier Valenzelektronen. Die Valenzen sind so ausgerichtet, dass sie zu vier flächendiagonal gegenüberliegenden Eckpunkten eines Würfels zeigen, in dessen Zentrum sich das Atom befindet [1.1]. Das daraus resultierende Diamantgitter kennzeichnet die Gitterstruktur von Silizium, deren Elementarzelle ein Würfel ist. Die Gitterstruktur von Silizium ist in Abb. 1.3a schematisch dargestellt.

**Abb. 1.3.** Gitterstruktur von Silizium (Diamantgitter) a) Räumliche Darstellung nach [1.1] und b) Ebenes Schema

Die Atome im Kristallgitter sind so angeordnet, dass jedes Atom ein Valenzelektron mit jedem der vier Nachbaratome teilt. Zur Vereinfachung der Darstellung verwendet man das in Abb. 1.3b abgebildete ebene Schema der Gitterstruktur.

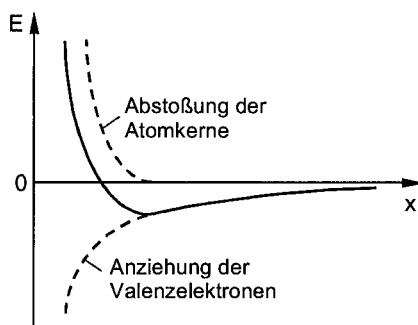

Die Wechselwirkung zwischen den Atomen im Kristallgitter wird charakterisiert durch abstoßende Kräfte zwischen den Atomkernen und anziehende Kräfte durch die Wechselwirkung der Valenzelektronen mit den Atomkernen. Die Bindungen im Kristallgitter ergeben einen optimalen Abstand der Atome, der durch den Zustand minimaler Energie charakterisiert wird. Die Bindungsenergie  $E$  im Kristallgitter in Abhängigkeit vom Abstand  $x$  der Atomkerne ist in Abb. 1.4 dargestellt.

**Abb. 1.4.** Bindungsenergie der Atome im Kristallgitter eines Halbleiters in Abhängigkeit vom Atomabstand

Auf Grund des aus der Bindungsenergie resultierenden, stabilen Abstandes der Atome im Kristallgitter und durch die gerichteten Valenzen entsteht unter geeigneten Bedingungen bei der Halbleitermaterialherstellung ein regelmäßiger Aufbau der Kristallstruktur.

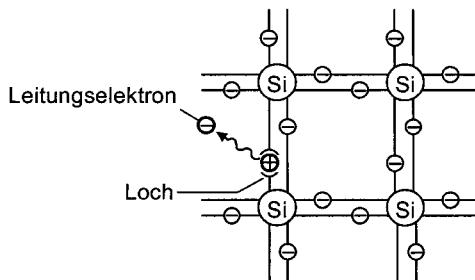

## 1.2.2 Eigenleitung

Die Eigenleitung tritt in vollkommen reinen Halbleitern auf. Diese Halbleiter werden *eigenleitende* oder *intrinsische* Halbleiter genannt. Durch thermische Gitterschwingungen brechen Bindungen des Kristallgitters auf und es entstehen *Elektron-Loch-Paare*. Dabei werden Valenzelektronen zu freien Elektronen (*Leitungselektronen*), die im Kristallgitter einen positiv geladenen Atomrumpf (*Loch*) hinterlassen. Wird dieses Loch durch ein Valenzelektron einer Nachbarbindung besetzt, so verschiebt sich das Loch an den neu entstandenen Platz der Nachbarbindung. Unter Einwirkung eines elektrischen Feldes ist also ein Stromfluss sowohl von Leitungselektronen als auch von Löchern möglich. Dieser als Eigenleitung bezeichnete Mechanismus beschreibt somit die Bewegung von Ladungsträgern im Kristall, wobei die *Ladungsträgerdichte*  $n$  der Elektronen und die Ladungsträgerdichte  $p$  der Löcher im Halbleitervolumen gleich ist ( $n = p$ ). Das

Prinzip der Eigenleitung ist in Abb. 1.6 im ebenen Schema der Silizium-Gitterstruktur veranschaulicht.

**Abb. 1.5.** Prinzip der Eigenleitung eines Halbleiters im ebenen Schema der Silizium-Gitterstruktur

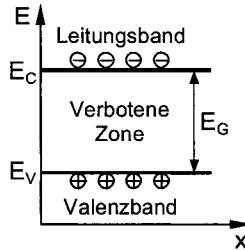

Die zur Bildung eines Elektron-Loch-Paars erforderliche Mindestenergie ist vom Halbleitermaterial und der Temperatur abhängig. Die Mindestenergie  $E_G$  beträgt bei  $T = 300\text{ K}$  für Silizium  $E_G = 1,1\text{ eV}$ , für Germanium  $E_G = 0,7\text{ eV}$  und für GaAs  $E_G = 1,4\text{ eV}$ .

Führt man dem Halbleiter Energie zu (z. B. thermisch oder optisch), so werden durch diese Energie Elektron-Loch-Paare generiert. Dieser Mechanismus wird *Generation* genannt. Der Generation von Elektron-Loch-Paaren wirkt nach Erzeugung einer bestimmten Ladungsträgeranzahl ein gegenläufiger Prozess entgegen. Dieser Prozess wird *Rekombination* genannt. Bei der Rekombination wird ein Leitungselektron von einem Loch eingefangen, wobei das Loch und das Elektron rekombinieren und Energie (z. B. thermisch oder optisch) freigesetzt wird. Bei konstanter Temperatur werden ständig Elektron-Loch-Paare generiert, wobei bereits generierte Ladungsträger gleichzeitig wieder rekombinieren. Bei konstanter Temperatur und ohne weitere Störungen durch z. B. elektrische oder magnetische Felder bildet sich dann ein Gleichgewicht aus, das als *thermodynamisches Gleichgewicht* bezeichnet wird. Die Ladungsträgerdichte  $n_0$  der Elektronen und die Ladungsträgerdichte  $p_0$  der Löcher im Halbleiter bei thermodynamischem Gleichgewicht ergeben sich zu:

$$n_0 = p_0 = n_i(T). \quad (1.1)$$

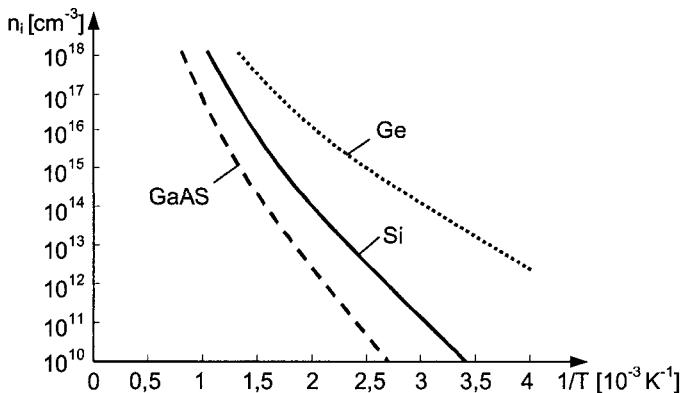

Dabei wird von einem *homogenen* Halbleiter ausgegangen, d.h. im Halbleiter existiert eine örtliche Gleichverteilung der Ladungsträger. Der Index Null der Ladungsträgerdichten  $n_0$  und  $p_0$  kennzeichnet den Fall des thermodynamischen Gleichgewichts. Die Größe  $n_i$  wird als *Eigenleitungsträgerdichte* oder intrinsische Ladungsträgerdichte bezeichnet. Sie beträgt bei  $T = 300\text{ K}$  für Silizium  $n_i \approx 1,5 \cdot 10^{10}\text{ cm}^{-3}$ , für Germanium  $n_i \approx 2,5 \cdot 10^{13}\text{ cm}^{-3}$  und für GaAs  $n_i \approx 1,8 \cdot 10^6\text{ cm}^{-3}$ . Die Eigenleitungsträgerdichte ist stark von der Temperatur abhängig. Diese Temperaturabhängigkeit ist in Abb. 1.6 für verschiedene Halbleitermaterialien abgebildet.

Abb. 1.6. Temperaturabhängigkeit der Eigenleitungsträgerdichte  $n_i$  für Ge, Si und GaAs

Die *Generationsrate*  $G$  definiert die Anzahl der erzeugten Elektron-Loch-Paare pro Zeit- und Volumeneinheit. Die thermische Generation ist in folgender Weise zum Bandabstand  $E_G$  und zum Produkt aus Temperatur  $T$  und Boltzmann-Konstante  $k$  proportional:

$$G(E_G, T) \sim \exp\left(-\frac{E_G}{k \cdot T}\right). \quad (1.2)$$

Die Rekombinationsrate  $R$  ist ebenfalls von der Temperatur abhängig und wird mit Hilfe der Ladungsträgerdichten und des *Rekombinationskoeffizienten*  $r$  wie folgt bestimmt:

$$R(T, n, p) = r(T) \cdot n \cdot p. \quad (1.3)$$

Der Rekombinationskoeffizient ist eine temperaturabhängige Materialkonstante, die das Produkt aus dem Wirkungsquerschnitt der Elektron-Loch-Wechselwirkung und der mittleren thermischen Geschwindigkeit der Ladungsträger darstellt [1.2].

Eine ungebrochene Bindung zerfällt bei Zuführen der Energie  $E_G$  in ein Leitungselektron und ein Loch. Umgekehrt gilt, dass ein Elektron-Loch-Paar bei Abgabe der Energie  $E_G$  in eine ungebrochene Bindung übergeht. Im thermodynamischen Gleichgewicht ist die Generationsrate gleich der Rekombinationsrate ( $G = R = r(T) \cdot n_0 \cdot p_0$ ) und es gilt:

$$n_0 \cdot p_0 = \frac{G(T)}{r(T)} = n_i^2(T). \quad (1.4)$$

Gl. (1.4) gilt nicht nur im Fall der Eigenleitung, sondern allgemein im thermodynamischen Gleichgewicht. Aus Gl. (1.4) resultiert weiterhin, dass die Erhöhung einer Ladungsträgerdichte (z. B.  $n_0$ ) zur Verringerung der anderen Ladungsträgerdichte ( $p_0$ ) führt. Dieser Aspekt wird in Abschn. 1.2.3 bei der Betrachtung des Störstellenhalbleiters genutzt.

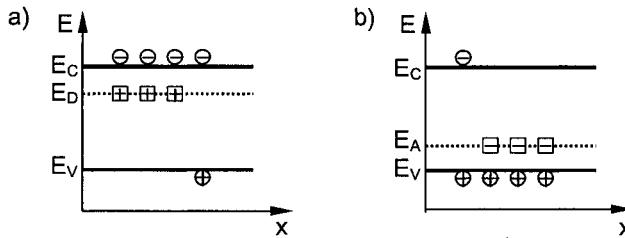

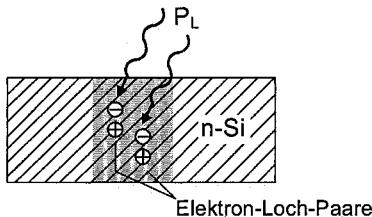

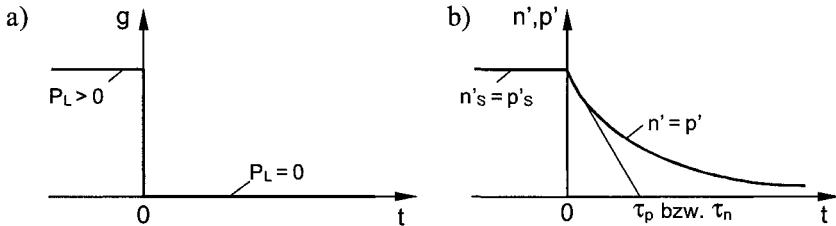

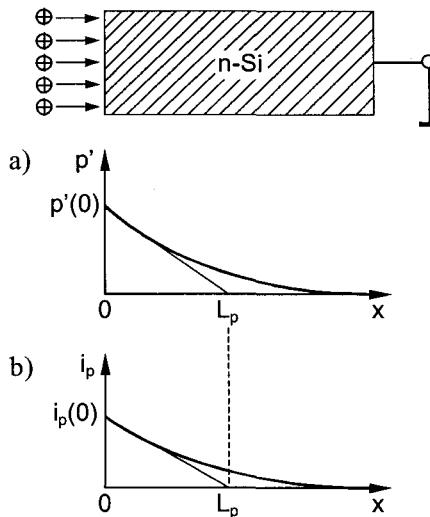

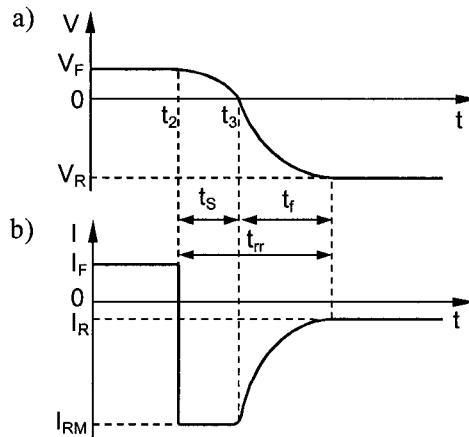

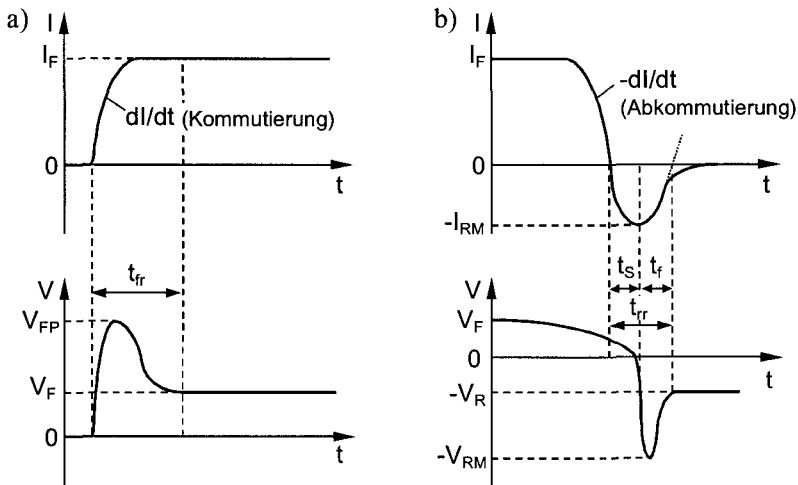

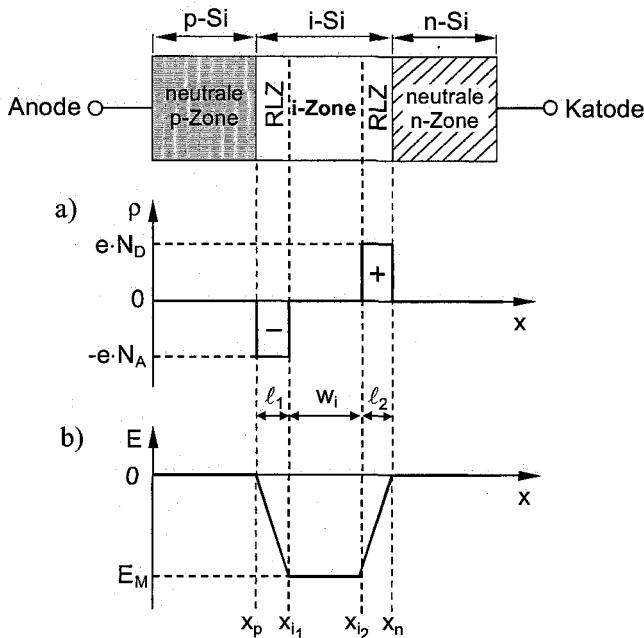

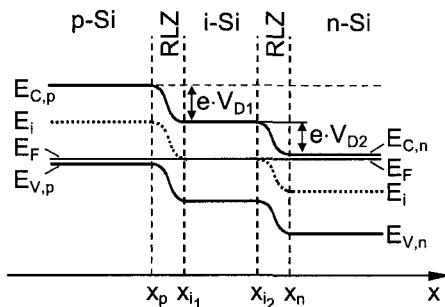

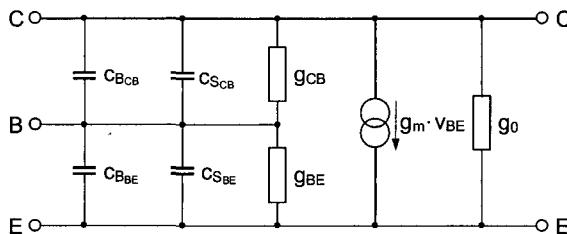

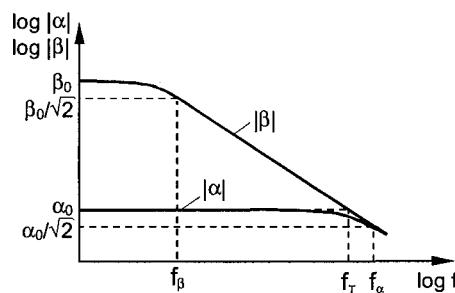

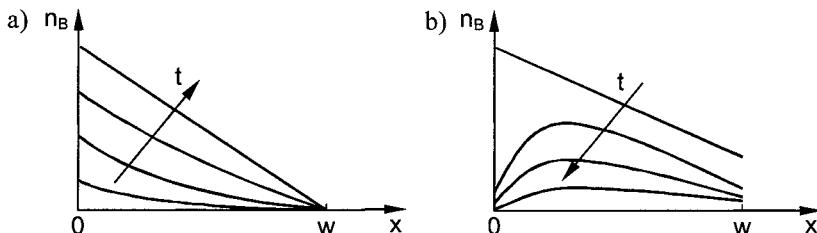

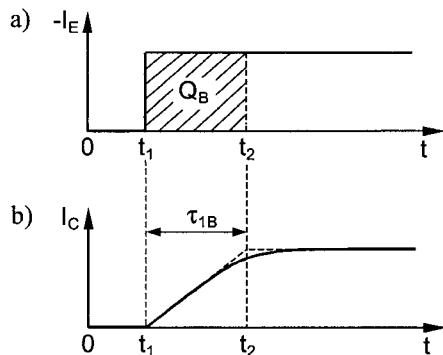

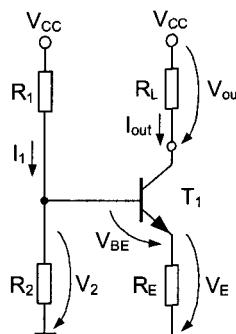

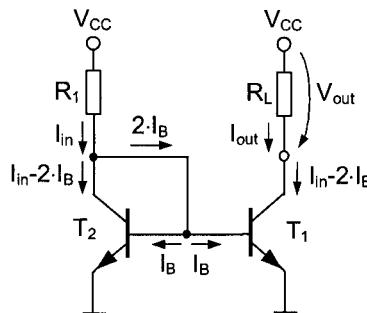

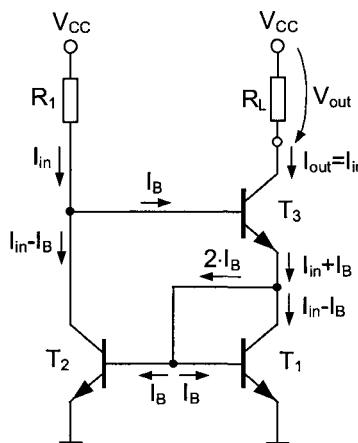

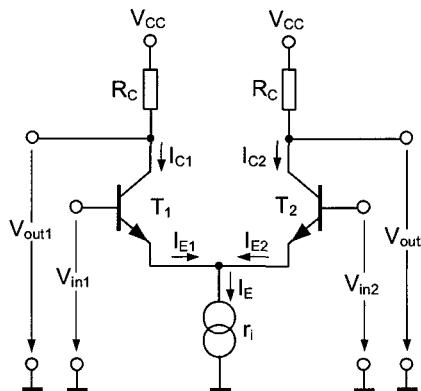

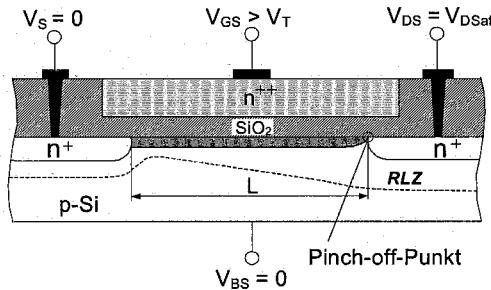

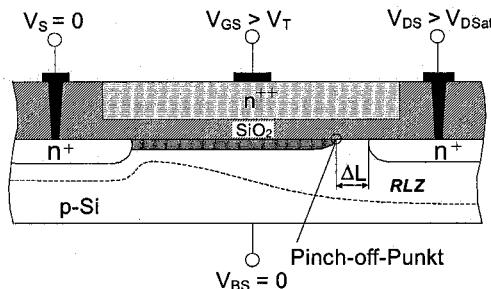

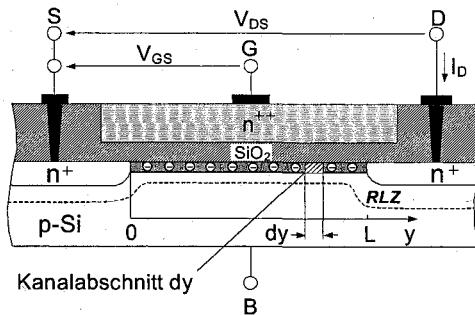

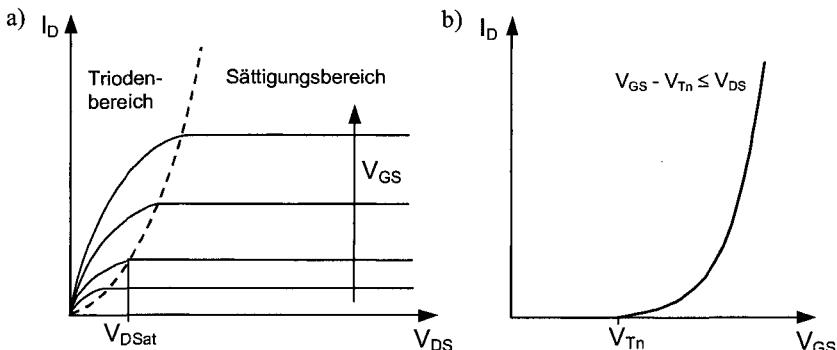

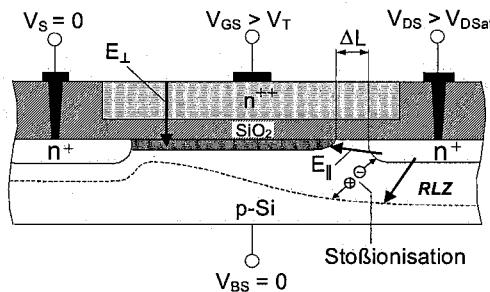

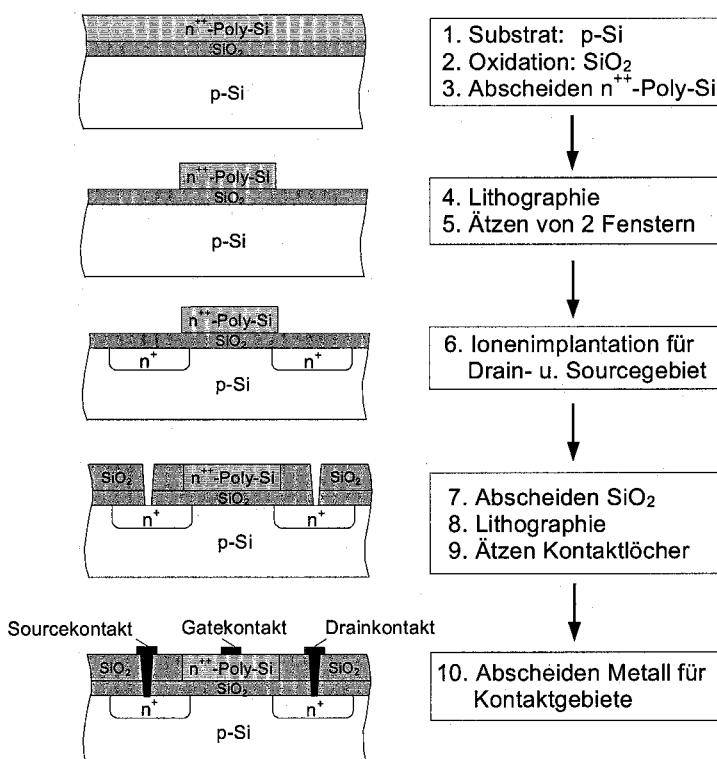

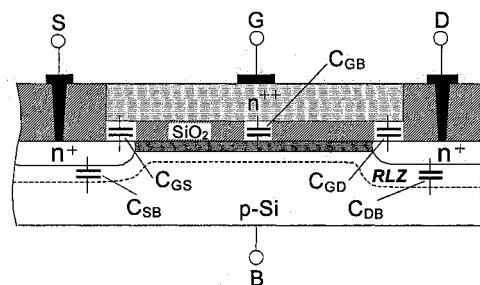

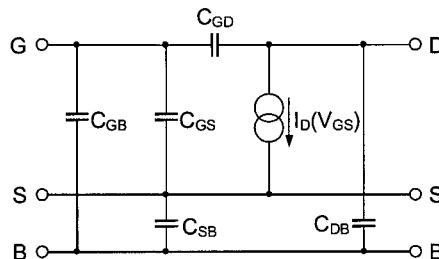

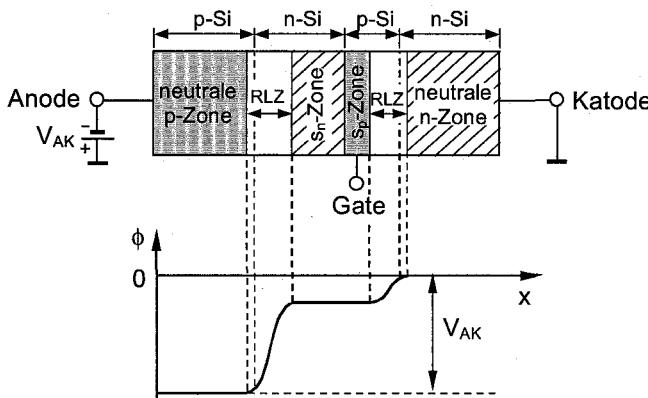

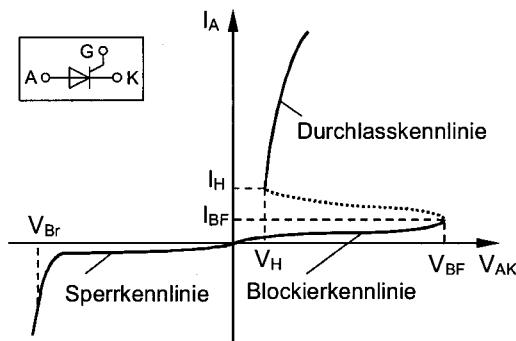

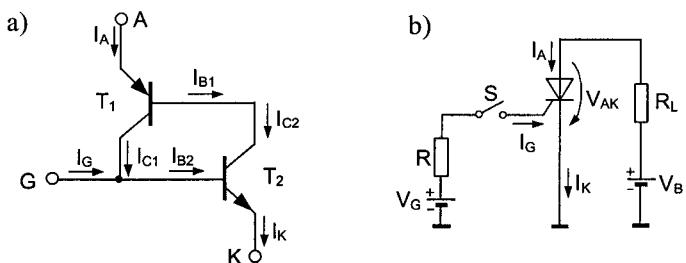

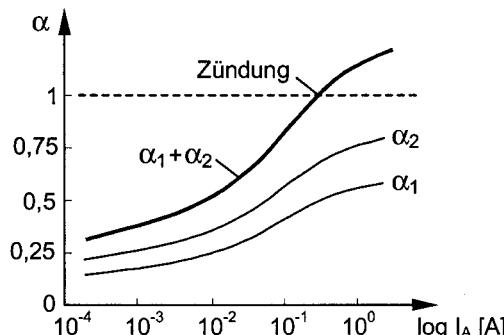

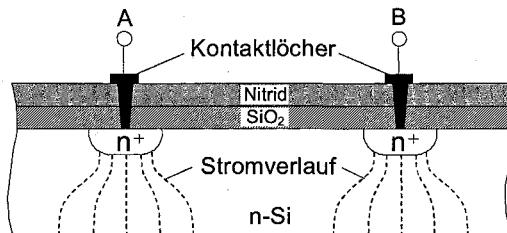

### 1.2.3 Störstellenleitung